13-06-2006 02:06:57 PM

Bab 1

Teknologi IC

Yang perlu diperhatikan dalam membuat suatu sistem rangkaian digital, selain sistem yang benar juga diperhatikan kecepatannya dan hemat daya.Untuk mempercepat rangkaiannya maka mobilitas elektronnya harus dipercepat. Supaya sistem tersebut cepat ada beberapa yang dapat dilakukan, antara lain :

1. Mengganti bahannya

2. Teknologi bahannya

3. Arsitekturnya

I.1 Bahan Pembentuknya

Bahan yang digunakan dalam membuat IC, pada dasarnya adalah silikon dan germanium, bahan yang dikomersialkan pertama kali adalah germanium dalam komponen bipolar. Tetapi kemudian beralih teknologi silikon.

Perbandingan antara Germanium dengan silikon :

|

Germanium |

Silikon |

|

1.Perpindahan elektron lebih cepat (0.39 sampai 0.19) 2.Karaktrisrik temperatur germanium lebih rendah dari siikon (lebih cepat panas) 3.lebih boros daya |

1.Perpindahan elektron lebih lama(0.14 sampai 0.05) 2. karakteristik Temperatur silikon lebih tinggi 3. lebih hemat daya |

I.2. Teknologi

Untuk mempercepat kinerja suatu rangkai dapat dilakukan dengan mengubah teknologi dari bahannya yaitu bipolar dan Mos. Adapun kedua kelebihan dan kekurangannya dari teknologi ini dapat dilihat di bawah ini :

1. TTL, merupakan ic logic yang paling cepat tapi merupakan ic yang boros energi.

2. C-MOS, merupakan ic yang mempunyai kecepatan sedang dan tidak terlalu boros.

3. XCL, merupakan ic yang paling lambat tapi paling hemat energi.

TTL adalah Transmitter Transistor Logic dimana transistor-transistornya bipolar. Dari ketiga contoh diatas yang sering digunakan adalah CMOS. Digital CMOS(Complementary Metal Oxide Semikonduktor) circuit yang digunakan sebagai pendorong bagi untuk perhitungan performance yang tinggi dan aplikasi engineering.

Sekarang diharapkan bahwa pengecilan ukuran IC CMOS dapar mencapai 0.15 mikrometer dalam satu decade. Dengan teknologi seperti ini, tingkat integrasi dalam sebuah Chip dapat menampung beberapa ratusan juta transistor untuk IC logic(logika) atau yang lebih tinggi dalam hal memory Chip,dimana hal ini menampilkan tantangan yang besar bagi perancang Chip Prosessor.

Teknologi lain yang digunakan adalah BiCMOS, Silicon-On-Isulator (SOI), GaAs. Sirkut Bipolar dan GaAs(Galium Arsenait) telah digunakan untuk Sirkuit dengan kecepatan tinggi.

Karena hal ini, teknologi MMICs(Monolithic Microwave Integrated Cicuits), GaAs MESFET(MEtal Semiconductor Field Effect Transistor) telah sukses, namun masih kurang efisien untuk VLSI atau ULSI (Ultra Large Scale Integration) karena prosesnya yang sulit dan mengkonsumsi tenaga yang besar.

IC dapat dibedakan menjadi 3 macam berdasarkan cara kerjanya :

§ IC digital, contoh : IC full adder

§ IC analog, contoh : IC OP-AMP

§ IC compound, contoh : IC ADC

Inisialisasi sejarah :

| 1948, transistor pertama dibuat. | |

| Pertengahan 1950, device diskrit tersedia untuk produk industri. | |

| Device yang pertama kali dikomersialkan adalah germanium junction bipolar transistor. | |

| Electron dan hole mobility dari germanium ( 0,39 dan 0,19 m2 v-1 s-1 ) > silicon ( 0,14 dan 0,05 m2 v-1 s-1 ). | |

| 1962, small scale integrated (SI) packages dengan 4 logic gates per package telah tersedia secara luas. |

Kelemahan transistor germanium :

| Temperatur lebih cepat panas dibandingkan silicon. | |

| Ketidakmampuan untuk mencegah transisi perimeter (metallurgical junction) antara p-regions dan n-regions yang sangat sensitive terhadap polusi oksigen atau uap air. | |

| Dibutuhkan bungkus yang sangat rapat untuk memberi reliabilitas jangka panjang. |

Silicon lebih sulit untuk diproses daripada germanium sehingga germanium secara komersial digunakan pertama kali.

Bipolar Vs MOS :

§ Lebih cepat daripada MOS tetapi lebih banyak membutuhkan daya.

§ Transconductance gm yang lebih besar sehingga memberikan signal amplification performance yang lebih baik.

§ Proses pabrikasi yang lebih sederhana.

§ CMOS memiliki impedansi yang lebih besar dibandingkan bipolar sehingga mengurangi power disipasi pada chip tetapi membatasi kemempuan untuk men-drive dan menaikkan waktu yang diperlukan untuk men-charge dan men-discharge kapasitansi sirkuit.

§ Device performance sangat bergantung pada geometri.

Kesimpulan :

| Bipolar selalu menjadi teknologi yang paling cepat. | |

| MOS selalu menjadi teknologi yang paling baik sehubungan dengan kepadatan chip dan konsumsi daya yang paling kecil. | |

| MOS merupakan teknologi yang dominan untuk rancangan memori. |

Teknologi yang lain :

| BiCMOS : Untuk menggabungkan masing-masing kelebihan dari bipolar dan CMOS pada satu chip. | |

| Silicon on isulator (SOI) : Untuk menggantikan bulk substrat silicon semikonduktor dengan substrat insulating, sapphire sering dipertimbangkan untuk hal ini. |

Keuntungan TTL :

| Banyak digunakan umum | |

| Lebih cepat |

Kerugian TTL :

| Konsumsi daya besar (10 mW per gate) | |

| Current spike tajam |

Schottky transistor : Pada waktu tegangan collector turun dan mencapai nilai saturasi, Schottky diaoda antara basis dan coleector akan konduksi, mencegah collector untuk turun lebih jauh hingga mencapai saturasi (VCE)

Emitter Coupled Logic (ECL)

Keuntungan :

§ Teknologi silicon yang tercepat untuk saat ini untuk sirkuit digital, hanya dapat diungguli oleh perkembangan galim-arsenide (Ga As).

Kelemahan :

§ Power disipasi yang tinggi sehingga membatasi jumlah gate per IC.

§ Voltage swing yang kecil sehingga menyulitkan interfacing dengan peralatan lain.

§ Membutuhkan sistem pendingin yang kompleks untuk sirkuit besar.

IC digital logic terdiri dari :

| RTL Resistor transistor logic | |

| DTL Diode transistor logic | |

| TTL Transistor transistor logic | |

| ECL Emitter coupled logic | |

| MOS Metal oxide semiconductor | |

| CMOS Complementary metal oxide semiconductor |

RTL dan DTL tidak lagi digunakan dalam desain sistem digital. RTL adalah family digital logic yang pertama kali digunakan secara komersial. Setelah itu, TTL menggantikan posisi DTL. TTL adalah modifikasi DTL sehingga TTL akan mudah dipelajari bila DTL telah dianalisa.

Dasar dari setiap IC digital logic family adalah NAND dan NOR gate. Kedua basic circuit ini membangun blok utama dari komponen digital yang kompleks.

Bipolar junction transistor (BJT) dapat berupa npn atau pnp junction transistor. Sebagai kontrasnya, field effect transistor (FET) disebut unipolar. Operasi dari bipolar junction bergantung dari dua tipe carrier, yaitu electron dan hole. Unipolar transistor bergantung pada dua tipe carrier mayoritas, yaitu electron (n-channel) dan hole (p-channel). Empat tipe pertama – RTL, DTL, TTL, dan ECL – menggunakan transistor bipolar. Dua family terakhir – MOS dan CMOS – menggunakan unipolar transistor disebut metal-oxide-semiconductor field- effect transistor, disingkat MOSFET atau MOS.

Bipolar Transistor Characteristics

Bipolar transistor memiliki dua tipe, yaitu npn atau pnp. Keduanya dibuat dari material yang sama, germanium atau silicon. IC transistor biasanya dibuat dengan silicon dan dengan tipe npn.

Contoh di atas adalah transistor npn yang menggunakan rangkaian common emitter. Rangkaian menggunakan dua resistor dan satu transistor. Arus IC mengalir melalui RC pada colector dan IB melalui RB pada basis. Emitter koneksi dengan ground dan IE = IC + IB. Supply voltase pada VCC dan ground. Input antara Vi dan ground, sedangkan output antara Vo dan ground.

Bila pada basis mengalir arus IB dan VBE positif, maka junction forward bias. Bila VBE negatif, maka junction reverse biased. Pada gambar diperlihatkan grafik VBE versus IB. Jika voltase basis-emitter kurang dari 0,6 V, transistor disebut dalam kondisi cut-off dan tidak ada arus basis yang mengalir. Saat base-emitter junction forward bias dengan voltase lebih besar dari 0,6 V, transistor conduct dan IB naik dengan cepat sedangkan VBE mengecil. Voltase VBE jarang melampaui 0,8 V.

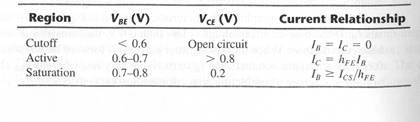

Arus yang kecil pada basis akan mengakibatkan arus yang lebih besar mengalir dari colector ke emitter. Ringkasan parameter transistor npn silicon dapat dilihat di tabel.

RANGKAIAN RTL DAN DTL

Gerbang Dasar Resistor Transistor Logic ( RTL )

Gambar 1.1 Suatu masukan gerbang RTL

Suatu gerbang RTL terdiri dari N transistor yang emitternya dihubungkan ke ground dan collectornya terhubung melelui tahanan collector yang sama kecatu daya. Tegangan input Vi ( i =1,2,N) menggambarkan level logika yang diberikan pada bese melalui tahanan Rb. Bila kita mangambil logika positif, gerbang memperlihatkan logika NOR.

|

V1 |

V2 |

V0 |

|

V1 |

V2 |

V0 |

|

L L H H |

L H L H |

H L L L |

0 0 1 1 |

0 1 0 1 |

1 0 0 0 |

Tabel 1.1 Logika NOR

Pada logika positif, “false” = 0 pada masukkan agar membuat transistor cut-off. VH adalah tegangan yang diberikan pada masukkan untuk membuat transistor saturasi. VL disini harus kurang dari tegangan tertentu dan VH harus lebih besar dari tegangan tertentu. Dalam hal ini VL < VH, tegangan cut-in dan VH > tegangan yang diberikan pada Rb yang membawa transistor pada keadaan saturasi.

Setiap input diimplementasikan dengan satu resistor dan satu transistor. Kolektor-kolektor dari masing-masing transistor dihubungkan menjadi satu pada output. Besar tegangan untuk rangkaian adalah 0,2 V untuk level low dan mulai 1 sampai 3,6 V untuk level high.

Analisis dari gerbang RTL sangat sederhana. Jika ada satu input gerbang RTL yang high, maka transistor yang bersangkutan akan menuju ke keadaan saturasi. Hal ini menyebabkan output akan low, tanpa perlu melihat keadaan transistor lain. Jika semua input low yaitu sekitar 0,2 V, maka semua transistor akan dalam keadaan cut off karena VBE < 0,6 V. Hal ini akan menyebabkan output dari rangkaian akan high, dengan besar tegangan mengacu pada tegangan VCC.

Gerbang Dasar Dioda Transistor Logic ( DTL )

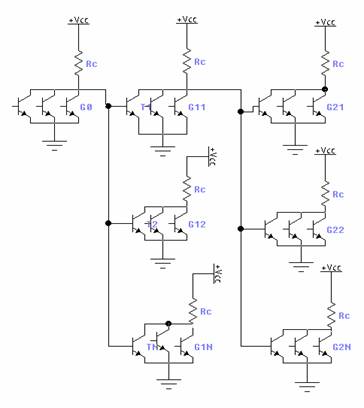

Dengan menghilangkan Rb pada rangkaian RTL maka terjadi Direct Coupled Transistor Logic (DCTL). Disebut DCTL karena masukkan dibuat langsung pada base. Seperti pada RTL diatas, DCTL ini merupakan logika NOR DTCL yang tidak banyak dipergunakan. Logika NOR mempunyai fungsi yang lengkap sehingga bermacam-macam logika dapat dibuat dengan memakai gerbang logika NOR. Di dalam system switching maka suatu input dari gerbang NOR dapat digerakan oleh keluaran dari gerbang NOR yang sama. Sebaliknya suatu gerbang NOR dapat dipakai untuk menggerakan masukkan gerbang Nor lainnya. Dalam hal ini contohnya adalah G11 pada gambar 1.2.

G11 menerima masukkan dari G0yang juga memberi sinyal pada salah satu masukkan dari gerbang (N-1) lainnya, yakni gerbang G12 sampai G IN. G11 ini juga memberikan sinyal pada salah satu dari gerbang N lainya, yakni G 21 sampai G 2N. gerbang-gerbang lainnya mendapat masukkan dari sumber lain yang tidak digambarkan pada gambar. Bila gerbang ini mempunyai kelebihan masukkan yang tidak dipergunakan, maka masukkan yang tidak dipergunakan harus digroundkan sehingga transistor yang bersangkutan akan berada pada cut-off dan tidak mempunyai pengaruh pada operasi gerbang.

Gambar 1.2 Gerbang DCTL NOR dengan N Fan-Out

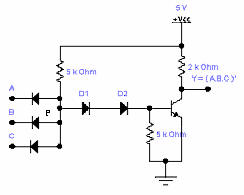

Rangkaian dasar dalam keluarga logika digital DTL adalah gerbang NAND. Tiap input diasosiasikan dengan sebuah dioda. Dioda dan resistor 5 kΩ membentuk sebuah gerbang AND. Transistor berperan sebagai penguat arus sambil meng-invert sinyal digital. Untuk logika low adalah sekitar 0,2 V dan untuk logika high adalah sekitar 4 sampai 5 V.

Jika salah satu input berlogika low atau sekitar 0,2 V, maka dioda input yang bersangkutan akan mengalirkan arus dari VCC dan melewati resistor 5 kΩ menuju input. Tegangan pada titik P adalah sama dengan tegangan input 0,2 V ditambah tegangan jatuh dioda 0,7 V, sehingga totalnya adalah 0,9 V. Agar transistor mulai aktif, tegangan pada titik P harus sekitar tegangan VBE ditambah tegangan jatuh dioda D1 dan D2 atau 3 X 0,6 V = 1,8 V. Karena tegangan pada titik P adalah sekitar 0,9 V, maka transistor dalam keadaan cut off dan output berlogika high atau sekitar 5 V.

Jika semua input dari gerbang adalah high, maka transistor akan menuju keadaan saturasi karena tegangan P sekarang sama dengan VBE ditambah tegangan jatuh D1 dan D2 atau 0,7 V X 3 = 2,1 V. Semua input dioda dalam keadaan reverse bias dan mati. Arus basis cukup besar untuk membuat transistor menuju ke keadaan saturasi, meskipun arus basis berkurang karena resistor 5 kΩ. Dengan keadaan transistor saturasi maka tegangan output akan jatuh menjadi sekitar VCE atau 0,2 V yang berarti logika low.

Transistor Transistor Logic ( TTL )

Ada 8 seri dari TTL, yaitu seperti tabel berikut :

|

Nama seri TTL |

Prefix |

Fan Out |

Power Dissipation (mW) |

Propagation Delay |

Speed Power Product (pJ) |

|

Standard |

74 |

10 |

10 |

9 |

90 |

|

Low Power |

74L |

20 |

1 |

33 |

33 |

|

High Speed |

74H |

10 |

22 |

6 |

132 |

|

Schottky |

74S |

10 |

19 |

3 |

57 |

|

Low Power Schottky |

74LS |

20 |

2 |

9,5 |

19 |

|

Advanced Schottky |

74AS |

40 |

10 |

1,5 |

15 |

|

Advanced Low Power Schottky |

74ALS |

20 |

1 |

4 |

4 |

|

Fast |

74F |

20 |

4 |

3 |

12 |

Gerbang TTL standard merupakan versi pertama dari keluarga TTL. Gerbang dasar ini kemudian dirancang dengan nilai resistor yang berbeda untuk menghasilkan gerbang dengan power dissipation yang lebig rendah namun dengan kecepatan yang lebih tinggi. Propagation delay dari sebuah rangkaian transistor dalam keadaan saturasi tergantung pada 2 hal, yaitu storage time dan konstanta waktu RC. Menurunkan storage time akan menurunkan propagation delay. Menurunkan nilai resistor akan menurunkan konstanta waktu RC. Tentu saja, trade-off nya adalah power dissipation yang lebih tinggi karena nilai resistor yang lebih rendah menyebabkan aliran arus yang lebih dari power supply. Kecepatan dari gerbang berbanding terbalik dengan propagation delay.

Pada gerbang low power TTL, nilai resistor lebih tinggi daripada gerbang standard untuk menurunkan power dissipation, tetapi propagation delay akan meningkat. Pada gerbang high speed TTL, nilai resistor diturunkan untuk mengurangi propagation delay, tetapi power dissipation meningkat. Gerbang Schottky TTL menjadi kemajuan berikutnya dibidang teknologi. Efek dari transistor Schottky adalah untuk menghilangkan storage time delay dengan menghindarkan agar transistor tidak saturasi. Seri ini meningkatkan kecepatan operasi tanpa peningkatan power dissipation yang terlalu besar. Low pwer Schottky TTL mengorbankan sedikit kecepatan untuk power dissipation yang lebih rendah. Ini sama dengan standard TTL pada propation delay, tetapi power dissipation-nya hanya seperlimanya dari standard TTL. Inovasi baru-baru ini telah membawa ke pengembangan dari seri advanced Schottky. Advanced Schottky menyediakan kemajuan dalam hal propagation delay dan power dissipation yang lebih rendah. Advanced low power Schottky merupakan speed power produk terlambat dan merupakan seri yang paling efisien. Keluarga fast TTL merupakan pilihan terbaik untuk rancangan dengan kecepatan tinggi.

Perbedaan dari seri TTL bukan karena logika digital yang dilakukan, tetapi lebih karena konstruksi internal dari gerbang dasar NAND. Gerbang TTL pada berbagai seri yang tersedia terbagi menjadi tiga tipe konfigurasi output :

1. Open-collector output

2. Totem-pole output

3. Three-state ( or tristate ) output

Contoh karakteristik Dari suatu IC:

TTL 74XX

|

Parameter |

Minimum |

Typical |

Maximum |

|

Vol |

- |

0.2 V |

0.4 V |

|

Vil |

- |

- |

0.8 V |

|

Voh |

2.4 V |

3.4 V |

- |

|

Vih |

2 V |

- |

- |

|

Iil = -1.6 mA |

Iih = 40 uA |

||

|

Iol = 16 mA |

Ioh = -400 uA |

||

Table 1

Karakteristik TTL 74XX

Arti dari karakteristik TTL ( Transistor-transistor logic ) tersebut adalah:

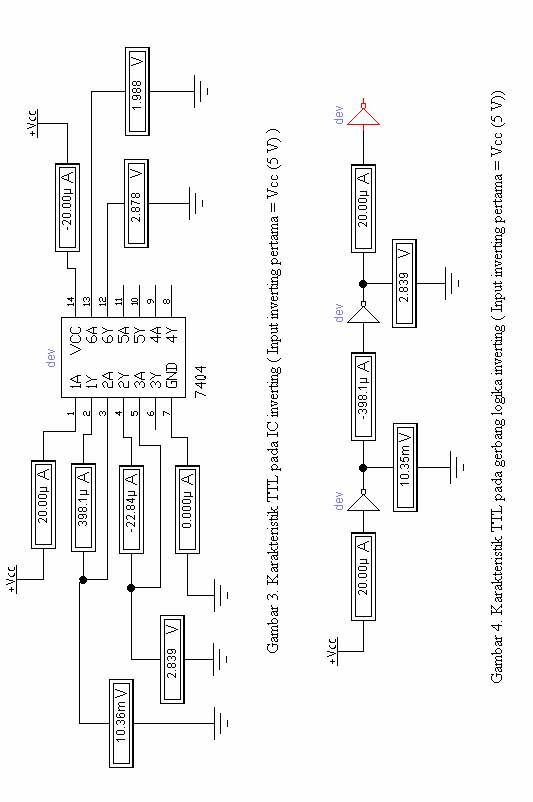

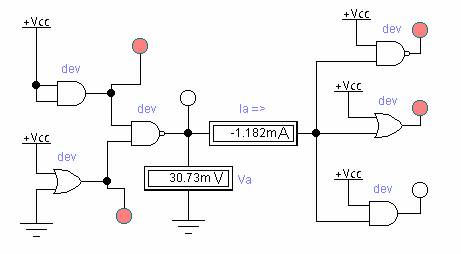

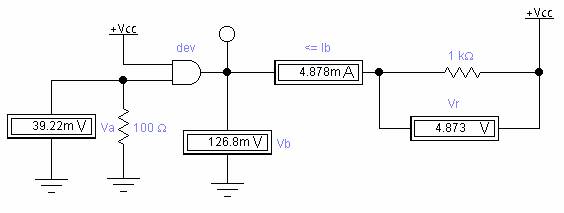

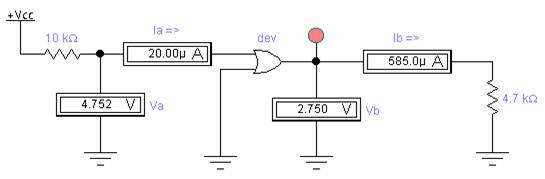

Contoh- contoh berikut ini menggunakan software Electronics Workbench, dengan masing – masing IC dan gerbang logic mempunyai karakteristik sebagai berikut :

Perbandingan antara penggunaan IC TTL dan gerbang logic pada software Electronics Workbench ini tidak terjadi perbedaan yang signifikan. Hal ini dibuktikan dengan perbandingan gambar 1 dan 2, serta gambar 3 dan 4.

Perbandingan antara gambar 1 dan 2 :

|

Inverter ke- |

IC |

Gerbang logic |

||

|

Input |

Output |

Input |

Output |

|

|

1 |

0 V |

2.839 V |

0 V |

2.839 V |

|

-400.3 uA |

20 uA |

-400.3 uA |

20 uA |

|

|

2 |

2.839 V |

10.36 mV |

2.839 V |

10.35 mV |

|

20 uA |

-398.1 uA |

20 uA |

-398.1 uA |

|

Table 3. Perbedaan antara gambar 1 dan 2

Perbandingan antara gambar 3 dan 4 :

|

Inverter ke- |

IC |

Gerbang logic |

||

|

Input |

Output |

Input |

Output |

|

|

1 |

5 V |

10.36 mV |

5 V |

10.35 mV |

|

20 uA |

-398.1 uA |

20 uA |

-398.1 uA |

|

|

2 |

10.36 mV |

2.839 V |

10.35 V |

2.839 mV |

|

-398.1 uA |

22.84 uA |

-398.1 uA |

20 uA |

|

Table 4. Perbedaan antara gambar 3 dan 4

Dari table dapat disimpulkan

Iih (Arus input Low) = 20uA

Iil (Arus input Hgh) = -398.1 uA = -0.3981 mA = 0.4 mA

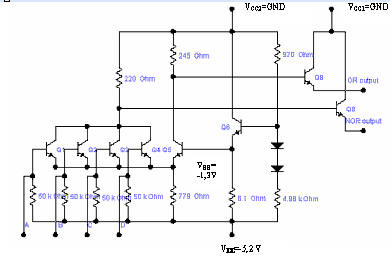

Emitter-Coupled Logic ( ECL )

ECL adalah keluarga logika digital yang nonsaturasi. Bila transistor tidak saturasi, dimungkinkan propagation delay yang rendah sebesar 1-2 ns. Keluarga logika ini memiliki propagation delay yang paling rendah dari keluarga digital lainnya, sehingga sering digunakan untuk sistem yang membutuhkan kecepatan tinggi. Namun ketahanan terhadap noise dan power dissipation merupakan yang terburuk daripada keluarga digital lainnya.

Rangkaian dasar ditunjukkan pada gambar dibawah ini. Output menyediakan operasi NOR dan OR sekaligus. Setiap input dihubungkan pada basis dari transistor. Untuk logika high tegangannya sekitar -0,8 V dan untuk logika low sekitar -1,8 V. Rangkaian terdiri dari differential amplifier, sebuah temperatur dan voltage-compensated bias network, dan emitter-follower output. Output emiter membutuhkan resistor pull-down agar arus dapat mengalir. Hal ini didapat dari resistor input RP dari gerbang lain yang mirip atau dari resistor eksternal yang dihubungkan dengan tegangan supply negatif.

Jika salah satu input dari ECL high, maka transistor yang bersangkutan akan nyala dan Q5 akan mati. Sebuah input -0,8 V menyebabkan transistor berkonduksi dan menempatkan -1,6 V pada emiter di semua transistor. ( tegangan jatuh VBE pada transistor ECL adalah 0,8 V ). Bila VBB = -1,3 V, tegangan basis dari Q5 hanya 0,3 V lebih positif dari emiternya. Q5 dalam keadaan cut off karena tegangan VBE membutuhkan minimal 0,6 V untuk berkonduksi. Arus pada resistor RC2 mengalir ke basis Q8. Arus tersebut sangat kecil sehingga tegangannya dapat diabaikan pada RC2. Output OR dari RC1 dan transistor yang berkonduksi menyebabkan tegangan jatuh sebesar 1 V dibawah ground atau sekitar -0,8 V. Output NOR adalah satu VBE dibawah level ini atau sekitar -1,8 V yang berarti logika low.

Jika semua input berlogika low, maka semua transistor akan mati dan Q5 akan berkonduksi. Tagangan pada simpul common-emiter adalah satu VBE dibawah VBB atau sekitar -2,1 V. jika basis setiap input berlogika low atau -1,8 V, setiap pasangan basis-emiter bertegangan 0,3 V dan semua input transistor dalam keadaan cut off. RC2 melewatkan arus melewati Q5 yang menghasilkan tegangan jatuh sekitar 1 V, membuat output OR satu VBE dibawah ini, pada -1,8 V atau level high. Hal ini menggambarkan operasi OR dan NOR pada rangkaian.

METAL OXIDE SEMICONDUCTOR (MOS)

Field effect transistor (FET) adalah transistor unipolar karena tergantung pada arus satu jenis pengangkut. Ada dua jenis field effect transistor: junction field effect transistor (JFET) dan metal oxide semi conductor (MOS). Dahulu digunakan di sirkuit linier dan belakangan digunakan pada sirkuit digital. Transistor MOS dapat dibuat lebih sederhana daripada transistor bipolar.

P-chanel MOS terdiri dari suatu bahan yang mengandung n-type silicon material. Dua daerah didifusi dengan p-type yang murni untuk membentuk sumber dan mengalirkan arus. Daerah antara kedua bagian p-typ bertindak sebagai saluran. Gerbang adalah plat metal yang terpisah dari chanel dielektrikum yang dibatasi oleh dioksida silisium. Suatu tegangan negatif di terminal gerbang menyebabkan suatu medan elektrik dalam saluran yang menarik pembawa p-type dari campuran. Ketika besar voltase negatif pada gerbang ditingkatkan, daerah di bawah gerbang pembawa ditingkatkan lebih positive, peningkatan daya konduksi, dan curent dapat mengalir dari sumber untuk mengalirkan, mengakibatkan suatu perbedaan voltase di antara dua terminal.

Ada 4 tipe dasar dari struktur MOS. Saluran dapat berupa p atau n type, tergantung dari apakah mayoritas carriers adalah hole atau electron. Model operasi dapat berupa enhancement atau depletion tergantung dari status daerah saluran pada tegangan gerbang nol. Jika saluran pada awalnya lebih kecil dengan p-type yang murni, saluran konduktor berada pada gerbang nol dan alat ini dapat dioperasikan pada mode depletion. Pada mode ini arus tidak mengalir kecuali jika saluran dihabiskan oleh suatu bidang gerbang yang diterapkan. Jika daerah di bawah gerbang ditinggalkan pada awalnya uncharged, saluran harus yang menyebabkan oleh bidang gerbang sebelum dapat mengalir. Kemudian arus saluran ditingkatkan oleh voltase gerbang dan dikatakan beroperasi dalam mode enhancement.

Sumber adalah terminal di mana mayoritas pembawa masuk palang itu. Saluran adalah terminal di mana pembawa utama meninggalkan bar itu. Pada P-Chanel MOS, sumber terminal terhubung pada substrate dan tegangan negatif diberlakukan bagi terminal saluran. Saat tegangan di gerbang adalah di atas voltase ambang pintu VT sekitar - 2V, tidak ada arus yang mengalir pada saluran dan saluran ke sumber alur seperti suatu sirkuit terbuka. Saat tegangan gerbang menjadi negatif di bawah VT, saluran dibentuk dan arus pembawa p-tipe dari sumber dialirkan. Pembawa p-tipe adalah positif dan sesuai dengan suatu sumber arus positif yang dialirkan.

Pada MOS n chanel, sumber terminal terhubung ke substrat dan tegangan positif diterapkan ke mengalirkan terminal. saat tegangan pada gerbang di bawah tegangan ambang pintu Vt sekitar 2V, tidak ada arus yang mengalir pada saluran. Saat tegangan pada gerbang terpenuhi positif di atas VT untuk membentuk saluran itu, pembawa n-tipe mengalirar dari sumber dialirkan. Pembawa n-tipe adalah negatif, bersesuaian dengan arus positif dialirkan dari sumber. Voltase ambang pintu mungkin bertukar-tukar dari 1-4V tergantung dari proses yang digunakan.

Simbol tipe enhancemen yang koneksi linenya terputus diantara sumber dan yang mengalirkan. Di dalam simbol substrte dapat diidentifikasikan dan terlihat terhubung ke sumber. Simbol alternatif menghilangkan substrte dan sebagai gantinya, panah ditempatkan di terminal sumber memperlihatkan untuk arah arus positif mengalir ( dari sumber untuk mengalirkan pada p-chanel dan dari mengalirkan ke sumber di n-chanel).

Karena kontruksi simetris dari sumber dialirkan untuk, MOS transistor dapat dioperasikan sebagai alat dari dua belah pihak. Walaupun umumnya dioperasikan sebagai arus pembawa dari sumber dialirkan, ada keadaan manakala adalah memungkinkan untuk mengijinkan arus pembawa dialirkan ke sumber.

Satu keuntungan dari MOS adalah dapat digunakan tidak hanya sebagai transistor tapi juga dapat berfungsi sebagai resistor. Resistor diperoleh Dari MOS secara permanen yang penyimpangan terminal gerbang untuk konduksi. Perbandingan sumber mengalirkan voltase arus saluran menentukan nilai berlawanan itu. resistor Yang lain mungkin dibuat dan dirakit dengan memperbaiki panjang dan lebar saluran dari MOS.

N-chanel MOS untuk suplai tegangan Vdd adalah positif sekitar 5V untuk mengijinkan arus sekarang positif dari saluran ke sumber. Dua voltase terukur adalah fungsi voltase ambang pintu VT. Tingkat rendah adalah di manapun dari 0 ke VT, dan cakupan dari VT ke VDD n-chanel gerbang tingkat tinggi biasanya menggunakan logika positif. P-Chanel MOS sirkuit menggunakan tegangan negatif VDD untuk mengijinkan aliran positif arus dari sumber untuk dialirkan. Dua mengukur tegangan adalah kedua-duanya di atas dan di bawah voltase ambang pintu VT negatif. P-chanel gerbang biasanya menggunakan logika yang negatif.

Sirkuit inverter dengan menggunakan MOS Q1 sebagai resistor Pembangkit dan Q2 sebagai resistor aktif. Mengisilah resistor MOS sebagai gerbang terhubung ke VDD menjaga selalu dalam keadaan diam. Saat masuk tegangan rendah VT, Q2 mati. Sejak Q1 selalu nyala keluaran dari tegangan adalah VDD saat masuk tegangan Vt Q2 nyala karena high. arus bergerak dari VDD melalui resistor beban Q1 Dan Menuju Q2 geometri dari dua MOS harus seperti tahanan dari Q2 itu, saat condukting sangat sedikit dibanding tahanan Dari Q1 itu untuk mengatur keluaran Y saat tegangan di bawah VT.

Gerbang NAND menggunakan transistor yang diseri. Input A dan B harus selalu tinggi semua transistor untuk menyalurkan dan menyebabkan keluaran menjadi rendah. apabila inputnya rendah transistor dimatikan dan outputnya yang bersesuaian tinggi. Rangkaian tahanan itu yang dibentuk oleh 2 Aktif MOS harus lebih kecil dari tahanan dari resistor pembangkit MOS. Gerbang NOR dapat menggunakan transistor paralel. Apabila input masuk besar, transistor mengalirkan dan keluarannya rendah yang bersesuaian. Apabila semua input rendah, semua transistor yang aktif akan mati dan keluarannya besar.

COMPLEMENTARY MOS ( CMOS )

CMOS circuit mengambil keuntungan dari fakta bahwa kedua-duanya n-chanel dan p-chanel dapat dibuat pada substrate CMOS sirkit terdiri dari berbagai macam tipe MOS sama yang saling behubungan untuk membentuk fungsi logic. Sirkuit dasar dari inverter terdiri dari p-chanel transistor dan satu n-chanel transistor. Sumber terminal Dari p-chanel adalah VDD dan sumber terminal dari n-chanel adalah ground. Nilai dari VDD mungkin berkisar antara + 3 sampai +18V. Dua ukuran tegangan adalah 0 V untuk tegangan rendah dan VDD untuk tegangan tinggi biasanya 5V.

Cara kerja dari inverter transistor MOS :

1. MOS n-chanel adalah saat gerbang nya ke sumber tegangan adalah positif.

2. MOS p-chanel adalah saat gerbang nya ke sumber tegangan adalah negative.

3. Tipe lainnya mati apabila tegangan dari gerbang ke sumber adalah nol.

Cara kerja dari inverter : Saat masuk rendah, kedua gerbang adalah nol. Masukan adalah pada VDD sehubungan dengan sumber dari p-chanel dan saat itu 0 V sehubungan dengan sumber n-chanel alat mati. Berdasar kondisi diatas mengakibatkan impedansi yang rendah alur Dari VDD ke keluaran dan impedansi yang tinggi dari keluaran ke ground. Oleh karena itu keluaran tegangan VDD tingkat tinggi di bawah kondisi-kondisi pemuatan normal. Saat masuk tinggi kedua-duanya gerbang adalah pada Vdd dan situasi dibalikkan, p-chanel mati dan n-chanel nyala. Hasilnya keluaran mendekati tingkatan rendah adalah 0.

Dua input Gerbang NAND dapat terdiri dari 2 p-tipe dan dua n-tipe unit paralel secara urut. Jika semua masukan high, kedua-duanya p-chanels transistor mati dan kedua-duanya n-chanel transistor Nyala Keluarannya adalah impedansi ke ground dan menghasilkan low status rendah. Bila ada input low, transistor n-chanel mati dan dihubungkan p-chanel transistor nyala keluaran dihubungkan digabungkan ke Vdd dan menuju state tinggi. Input berbagai Gerbang NAND mungkin yang dibentuk dengan menempatkan nomor ;jumlah p-tipe dan n-tipe transistor paralel dan seri , berturut-turut, di suatu pengaturan similiar.

Dua-Input gerbang NOR terdiri dari 2 jenis n-type unit yang paralel dan dua p-type unit yang diseri. Saat semua masuk low dua p-chanel unit nyala dan dua n-chanel mati. Keluaran digabungkan ke Vdd dan menuju ke status yang high. Apabila semua input high, transistor p-chanel akan mati dan dihubungkan transistor n-chanel hidup dihubungkan. Ini menghubungkan output ke ground yang menyebabkan outputnya menjadi rendah.

Transistor MOS dapat dipertimbangkan berfungsi sebagai salah satu tombol elektonik yang melakukan atau bersikap terbuka. Sebagai contoh inverter CMOS dapat divisualisasikan sebagai dua tombol. Menerapkan masukan tegangan rendah menyebabkan switch bagian atas ( p) untuk menutup menyediakan suatu tegangan tinggi kepada keluaran. Menerapkan tegangan tinggi ke masuk menyebabkan switch yang lebih rendah ( n) mentup hubungan output ke ground, demikian kemudian Keluaran Vout adalah komplemen dari input Vin itu. Aplikasi komersil sering menggunakan lambang grafik lain transistor MOS untuk untuk menekankan perilaku logis switch itu. Panah menunjukan arah arus mengalir yang dihilangkan.

Sebagai gantinya, gerbang dari transistor p-chanel digambarkan dengan gelembung inverter di gerbang terminal menunjukan bahwa itu dimungkinkan dengan tegangan rendah. Suatu logika 0 dalam masukan menyebabkan transistor bagian atas untuk melakukan membuat logika output 1. Suatu logika 1 dalam masukan memungkinkan transistor menggunakan logika output yang lebih rendah 0.

Karakteristik CMOS

Saat sirkuit logik CMOS dalam keadaan diam power disipasinya rendah. Ini terjadi karena ada selalu suatu batal/mulai transistorin alur dimana status sirkit tidak berubah. Seperti hasilnya, gerbang CMOS mempunyai power disipasi yang tetap sekitar 0.01 mW. bagaimanapun juga , saat sirkuit berubah diam sebesar 1Mhz, kekuatan disipasinya bertambah sekitar 1mW dan di 10 Mhz sekitar 5mW.

CMOS logika pada umumnya ditetapkan untuk power suplai tunggal menyediakan operasi di atas suatu voltase mencakup dari 3 ke 18 V dengan nilai VDD sekitar 5V. Nyalakan CMOS di tegangan power suplai mengurangi propagasi delai waktu dan meningkatkan margin noise tetapi power disipasinya bertambah. Waktu propagasi delai dengan VDD adalah 5V dengan waktu dari 5 ke 20ns tergantung tipe yang digunakan. noise margin biasanya sekitar 40 persen dari tegangan untuk menggerakkan suplai. Fan keluaran dari gerbang CMOS adalah sebesar 30 saat frekuensi sebesar 1 MHZ fan keluaran berkurang seiring dengan kenaikan pada frekuensi operasinya.

Ada beberapa tipe dari IC CMOS. Seri 74C dan fungsinya kompatibel dengan IC TTL mempunyai nomer yang sama. Sebagai contoh IC CMOS tipe 7aC04 mempunyai 6 inverrter dengan konfigurasi letak Yang sama dengan IC TTL tipe 7404. CMOS dengan kecepatan tinggi 74HC adalah pengembangan dari 74C seri dengan penambahan suatu di kecepatan swith sepuluh kali lipat. 74HCT rangkaian secara elektris kompatibel dengan IC TTL. Ini berarti sirkuit seri ini dapat dihubungkan dengan input dan output Dari IC TTL tanpa harus menggunakan tambahan sirkuit alat penghubung. Versi terbaru dari CMOS adalah seri 74HC dengan kecepatan tinggi dan TTL ini kompatibel dengan versi 74HCT.

Bab II

Rangkaian Logic

Dalam format yang paling umumnya, suatu kombinasi rangkaian logika, atau gate,

melakukan suatu fungsi Boolean dapat diwakili sebagai multiple-input

single-output sistem. Semua variabel input diwakili oleh voltase node, mengacu

pada potensial ground. Penggunaan positive logic convention, Boolean (atau

logika) nilai "1" dapat diwakili oleh suatu tegangan tinggi

![]() , dan Boolean (atau logika) nilai "0" dapat diwakili oleh

suatu voltase rendah 0. Node output di load dengan suatu kapasitansi

, dan Boolean (atau logika) nilai "0" dapat diwakili oleh

suatu voltase rendah 0. Node output di load dengan suatu kapasitansi

![]() , yang mana mewakili kapasitansi parasitic device yang

dikombinasikan di dalam sirkit dan komponen kapasitansi saling behubungan yang

dilihat oleh node output. Output ini load kapasitansi pasti yang memiliki peran

yang sangat penting dalam operasi dinamis menyangkut gate logika.

, yang mana mewakili kapasitansi parasitic device yang

dikombinasikan di dalam sirkit dan komponen kapasitansi saling behubungan yang

dilihat oleh node output. Output ini load kapasitansi pasti yang memiliki peran

yang sangat penting dalam operasi dinamis menyangkut gate logika.

Pada bab ini akan dibahas mengenai inverter, BCD, error parity, dan ALU.

II.1 Rangkaian Inverter

Dikasih 5V, maka Output 0V

Dikasih 0V, maka Output Vcc

AB+C = AB.C = AB.C

Dari gambar dapat kita simpulkan, apabila rangkaian tersebut diberi tegangan 5V, 1V maka outputnya akan 0V. Jika rangkaian tersebut diberi tegangan 0V maka outputnya berupa Vcc.

Selain rangkaian logika di atas, masih terdapat banyak rangkaian inverter yang lain seperti dibawah ini :

Dari rangkaian inverter diatas jika Vin di kasih 0 ( low ) maka Vout akan menjadi 1( high ) dan juga sebaliknya, jika Vin diberi 1 maka Vout akan menjadi 0. Dari ketiga teknologi diatas dapat di lihat bahwa yang paling lambat adalah PMOS dan NMOS dan paling boros daya karena arus akan terus mengalir, tetapi paling murah. Contohnya NMOS inverter, jika diberi 1 maka NMOS akan ON dan arus dapat terus mengalir dari Vdd, sedangkan pada CMOS inverter arus tidak mengalir karena PMOS off.

Berikut ini adalah beberapa contoh gerbang logika :

Hukum De Morgan

XOR (ERROR PARITY )

Jika jumlah 1 ganjil maka akan keluar 1

01 jumlah 1 ganjil maka keluar 1

11 jumlah 1 genap maka keluar 0

Pada gambar pertama, forward sehingga 5V dapat terkirim

|

V1 |

V2 |

Vo |

|

0 |

0 |

0 |

|

0 |

5V |

5V |

|

5V |

0 |

5V |

|

5V |

5V |

5V |

BCD

BCD merupakan penjumlahan dimana bila hasilnya lebih dari 9 maka harus ditambah 6 agar hasilnya benar.

Contoh:

S4 S3 S2 S1

1 0 1 0 = 10 Faktor koreksi diperlukan bila:

1 0 1 1 = 11 1. nilai lebih dari 9

1 1 0 0 = 12 2. terdapat carry

1 1 0 1 = 13

1 1 1 0 = 14

1 1 1 1 = 15

Data diatas perlu dilakukan koreksi.

F = S3S4 + S2S4

F = S4 (S3+S2)

IC 7485 merupakan komparator 4 bit , misal : A=B berarti pin A=B :1

I1 I0 Y0 Y1 Y2 Y3 S1 S0=selector

Y0 = 0 0 1 0 0 0

Y1 = 0 1 0 1 0 0

Y2 = 1 0 0 0 1 0

Y3 = 1 1 0 0 0 1

ALU ( ARITHMATIC LOGIC UNIT )

ALU merupakan arithmetic atau logic tergantung input n.

|

S3 |

S2 |

S1 |

S0 |

M=high |

M=low |

|

0 |

0 |

0 |

0 |

F=A |

F=A |

|

0 |

0 |

0 |

1 |

F=A+B |

F=A+B |

|

0 |

0 |

1 |

0 |

F=AB |

F=A+B |

Bab III

Gerbang Logic

Pada bab ini akan dibahas mengenai berbagai macam rangkaian logika dengan kombinasi berbagai gerbang logika seperti AND, OR, NOR, NAND dan NOT.

Data

IoH = -400µA (max)

IIH = 40µA (max)

Catatan:

IOH = arus output HIGH

IIH = arus input HIGH

Tanda (-) berarti keluaran IC

Pada saat logic LOW

Data IOL = 16 mA (max)

IIL = -1,6 mA (max)

Jadi fade out = IOL / IIL = IOH / IIH

VOL = untuk tegangan max pada saat logic nol hanya sampai 0.4V

VOH = untuk tegangan max pada saat logic high todak kurang dari 2.4V

VIL = tegangan input low hanya max 0.8V

VIH = tegangan pada input high min 2.0V

1. Dari soal dibawah tentukan :

a. Va ?

b. Ia ?

Jawab :

Keterangan :

a. Va = 0.2 V karena output dari gerbang NAND menghasilkan output 0 (Low) sehingga dari data book yang ada dibawah, maka nilai tegangan yang diambil adalah VOL yang typical.

b. Ia = IIL (NAND) + IIL (OR) + IIL (AND)

= 1.6mA + 1.6mA + 1.6mA

= 4.8mA.

2. Dari soal dibawah tentukan :

a. Va, Vb dan Ib?

Keterangan :

a.

![]()

![]()

![]()

![]()

![]()

b. Vb= 0.2V karena output dari gerbang AND adalah Low.

c.

![]()

3. Dari soal dibawah tentukan :

· Va, Vb dan Ib?

Keterangan:

· Vx = IIH x 10k ohm

= 40μA x 10k ohm

= 0.4V

Va = 5 – Vx

= 5 - 0.4

= 4.6V

· Vb = VOH = 3.4V (karena output yang dihasilkan adalah High)

· Ib = Vb x 4.7k ohm

= 3.4V x 4.7k ohm

= 723μA

Dibawah ini merupakan data sheet IC untuk gerbang logika diatas :

|

Parameter |

Minimum |

Typical |

Maximum |

|

VOL |

- |

0.2V |

0.4V |

|

VIL |

- |

- |

0.8V |

|

VOH |

2.4V |

3.4V |

- |

|

VIH |

2V |

- |

- |

|

IIL = -1.6mA |

IIH = 40μA |

||

|

IOL = 16mA |

IOH = -400mA |

||

VOL = untuk tegangan max pada saat logic nol hanya sampai 0.4V

VOH = untuk tegangan max pada saat logic high tidak kurang dari 2.4V

VIL = tegangan input low hanya max 0.8V

VIH = tegangan pada input high min 2.0V

Power Dissipation

Arus disipasi ada dua macam yaitu :

Rumus Power Dissipation :

|

|

Dimana :

|

|

Contoh soal:

IC 7402 NOR dengan IccL = 14mA dan IccH = 8mA.

Tentukan besarnya Power Dissipation !

Jawab:

Vcc = 5V

![]()

=

![]()

=

![]()

= 11mA.

![]()

![]()

= 55 mWatt.

Noise Margin

Sinyal elektrik dari industri dan sumber lain yang serupa dapat menimbulkan voltase yang tidak diinginkan dalam logic sircuit. Sinyal yang tidak diinginkan ini disebut sebagai noise. Ada dua tipe noise yang perlu dipertimbangkan, yaitu DC noise yang ditimbulkan oleh drift pada level voltase sinyal. AC noise adalah pulsa random yang mungkin diciptakan oleh switching sinyal lain. Noise margin adalah voltase noise maksimum yang ditambahkan pada sinyal input digital circuit agar tidak menimbulkan perubahan yang tidak diinginkan pada output. Kemampuan untuk dapat beroperasi pada lingkungan yang memiliki banyak noise sangatlah penting untuk berbagai aplikasi. Noise margin dinyatakan dalam volt dan merepresentasikan sinyal maksimum noise yang bisa ditolerir oleh gate.

Parameter noise standar untuk TTL NAND gate adalah

VOH = 2,4 v VIH = 2 v

VOL = 0,4 v VIL = 0,8 v

High state noise margin = 2,4 – 2 = 0,4 v

Low state noise margin = 0,8 – 0,4 = 0,4 v

Resistor Pull-Up

Pada rangkaian diatas, Rpull-up tidak boleh terlalu besar dan juga tidak boleh terlalu kecil. Jika terlalu kecil, maka arus yang mengalir dari Vcc yang sangat besar akan mengakibatkan transistor Q4 akan rusak.

Jika Rpull-up terlalu besar, maka outputnya seolah-olah mengambang karena hambatan terlalu besar sehingga arus dari Vcc tidak dapat mengalir.

OC biasanya dipakai untuk arus yang besar. Selain itu juga untuk membuat AND gate.

Contohnya dapat dilihat dari gambar dibawah ini:

Jawab :

Jadi

persamaan X =![]() •

• ![]() •

•![]()

Untuk mencegah terjadinya EMI (Electromagnetik Interference) maka kaki dari gerbang logika yang tidak dipakai dihubungkan ke Ground (GND) atau ke Vcc.

Untuk gerbang AND dan NAND, kaki yang tidak dipakai dihubungkan ke Vcc. Sedangkan untuk gerbang OR dan NOR, kaki yang tidak dipakai dihubungkan dengan GND.

Pada IC, untuk kaki yang tidak dipakai, maka kaki tersebut harus dihubungkan tergantung dari outputnya. Tujuannya adalah untuk penghematan energi karena untuk pemakaian arus yang kecil. Jika outpunya High maka harus dihubungkan ke Vcc. Untuk output yang Low maka harus dihubungkan ke Ground.

Jenis-jenis IC :

1. 74HXX

Jenis IC ini, lebih cenderung ke arah high speed karena R nya diturunkan sehingga speed naik menjadi 2 (dua) kali lipatnya. Akibatnya propagation delaynya menjadi ½ nya. Dimana propagation delay = R×C.

2. 74LXX

Jenis IC ini lebih cenderung ke arah low power (hemat daya) karena R nya dinaikkan maka Power turun menjadi ½ nya. Akan tetapi propagation delaynya menjadi 2 kali lipat dari biasanya.

3. 74SXX

Propagation delay pada IC ini diturunkan menjadi ¼ nya dan Power dinaikkan menjadi 2 kali lipatnya. IC jenis ini lebih baik daripada IC jenis 74LXX.

4. 74LSXX

Konfigurasi dari IC ini jika dibandingkan dengan IC jenis 74SXX maka IC ini 1/3 dari IC jenis 74SXX. Tapi jika dibandingkan dengan IC jenis 74XX maka IC ini hanya 1/5 dari IC jenis 74XX.

5. 74ALSXX.

IC ini merupakan peningkatan dari IC jenis 74LSXX (Advanced Low Power Schottky).

6. 74FXX

Tiap transistor dalam chip harus cukup diisolasi agar tidak terjadi short circuit. Isolasi dapat menggunakan PN junction dengan diberi reverse bias. Akan tetapi pada 74FXX diisolasi menggunakan osilator (berupa oxide).

Menghubungkan beberapa IC arusnya tidak boleh melebihi melebihi nilai yang tercantum pada data sheet.

Contoh :

Data

IoH = -400µA (max)

IIH = 40µA (max)

Catatan:

IOH = arus output HIGH

IIH = arus input HIGH

Tanda (-) berarti keluaran IC.

MOSFET

Keterangan :

P-Channel akan ON jika input yang diberikan Low dan akan OFF jika inputnya High. Sedangkan N-Channel akan ON jika input yang diberikan High dan akan OFF jika inputnya Low.

Contoh :

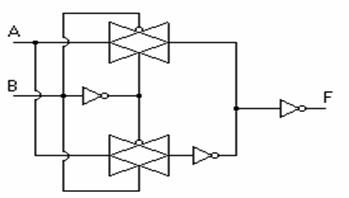

1. Analisa gambar rangkaian dibawah ini, kemudian tentukan gerbang apakah rangkaian tersebut!

Jawab:

|

A |

B |

P |

N |

Y |

||

|

Q1 |

Q2 |

Q3 |

Q4 |

|||

|

0 |

0 |

ON |

ON |

OFF |

OFF |

1 |

|

0 |

1 |

ON |

OFF |

OFF |

ON |

1 |

|

1 |

0 |

OFF |

ON |

ON |

OFF |

1 |

|

1 |

1 |

OFF |

OFF |

ON |

ON |

0 |

≈ Jadi rangkaian diatas merupakan rangkaian gerbang NAND.

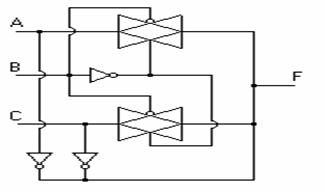

2. Analisa gambar rangkaian dibawah ini, kemudian tentukan gerbang apakah rangkaian tersebut!

Jawab:

≈ Jadi rangkaian diatas merupakan rangkaian gerbang NOR.

Data book IC

|

Keterangan |

7404 |

4069B |

|

VOL max |

0.05V |

0.4V |

|

VIL max |

1.67V |

0.8V |

|

VIH min |

3.33V |

2V |

|

VOH min |

4.95V |

2.4V |

|

IIH max |

1μA |

40μA |

|

IIL max |

-1μA |

-1600μA |

|

IOH max |

-0.51mA |

-0.4mA |

|

IOL max |

0.51mA |

16mA |

Dimana OL = Output Low

IL = Input Low

IH = Input High

OH = Output High

Berdasarkan Data Book IC diatas maka analisa apakah TTL dan CMOS dibawah ini bisa dihubungkan?

Jawab:

Syarat agar kedua IC tersebut dapat dihubungkan adalah dilakukan analisa terhadap segi tegangan dan arus.

Dilihat dari tegangannya :

Keterangan :

Pada TTL 7404 jika menghasilkan output tegangan low maka akan menghasilkan tegangan sebesar 0.4V. Agar bisa dihubungkan, maka tegangan output dari TTL 7404 harus masih bisa dibaca oleh CMOS 4069B sebagai Low juga. Karena tegangan input low dari CMOS 4069B paling maksimum adalah 1.67V maka 0.4V dari TTL masih dianggap low oleh CMOS 4069B. Jadi kesimpulannya, pada level tegangan low, kedua IC ini bisa dihubungkan.

Keterangan:

Pada TTL 7404 jika menghasilkan output tegangan high maka akan menghasilkan tegangan sebesar 2.4V. Agar bisa dihubungkan, maka tegangan output dari TTL 7404 harus masih bisa dibaca oleh CMOS 4069B sebagai high juga. Karena tegangan input high dari CMOS 4069B paling minimum adalah 3.33V maka 2.4V dari TTL tidak dianggap high oleh CMOS 4069B. Jadi pada level tegangan high, kedua IC ini tidak bisa dihubungkan. Untuk mengatasi keadaan diatas, maka digunakan resistor pull up yang bermanfaat untuk menaikkan tegangan di TTL 7404 sehingga bisa dibaca oleh CMOS 4069B sebagai high.

Lihat gambar dibawah :

Dengan adanya tambahan Rpull-up maka tegangan output dari TTL 7404 akan naik karena adanya tambahan 5 volt dari Rpull-up, sehingga tegangan output dari TTL 7404 akan terbaca high oleh CMOS 4069B. Jadi, dengan adanya Rpull-up, maka kedua IC dapat dihubungkan.

Dilihat dari arusnya :

Keterangan:

Pada TTL 7404 jika menghasilkan output arus low maka akan menghasilkan arus sebesar 16mA. Agar bisa dihubungkan, maka arus output dari TTL 7404 harus bisa menampung jumlah arus yang dikeluarkan oleh CMOS 4069B. Karena arus input low dari CMOS 4069B paling maksimum adalah 1μA maka TTL masih bisa menampung arus dari CMOS 4069B yang hanya sebesar 1μA. Jadi kesimpulannya, pada level arus low, kedua IC ini bisa dihubungkan.

Keterangan:

Pada TTL 7404 jika menghasilkan output arus high maka akan menghasilkan arus sebesar 0.4mA. Agar bisa dihubungkan, maka arus output dari TTL 7404 harus bisa menyediakan jumlah arus yang dibutuhkan oleh CMOS 4069B. Karena arus input low dari CMOS 4069B paling maksimum adalah 1μA maka TTL masih bisa menyediakan arus yang dibutuhkan CMOS 4069B yaitu sebesar 1μA. Jadi kesimpulannya, pada level arus high, kedua IC ini bisa dihubungkan.

Kesimpulan: Kedua IC bisa dihubungkan.

Level Shifter

Bab IV

Karakteristik Rangkaian Flip Flop

Dalam rangkaian flip-flop yang ideal input, clock dan output selalu terletak bersamaan, tetapi pada kenyataannya hal ini tidak akan pernah terjadi karena adanya setup time ( ts(h) dan ts(l) ) hold time ( th(h) dan th(l) ), time propagation ( tphl dan tplh ) dan clock pulse wave ( tw(h) dan tw(l) ). Jika input dan clock terletak bersamaan maka output akan undefined.

Pada bab ini akan dibahas mengenai karakteristik dari flip-flop, meliputi time propagation, hold time dan setup time.

IV.1 Time Propagation

Time propagation merupakan waktu yang diperlukan output untuk berubah setelah terjadi clock. Setelah terjadi clock output tidak akan langsung berubah dari high ke low atau dari low ke high melainkan terjadi delay beberapa waktu baru berubah.

Untuk mengetahui besarnya time propagation dilihat dari perubahan yang terjadi pada input dan output pada tegangan 1.5V.

Contoh soal :

Dari data book IC didapat tpLH = 22ns dan tpHL = 15ns. Gambarkan pulsa input dan outputnya.

Jawab:

Translator

IV.2 Setup time (ts) dan Hold time (th)

Setup time adalah waktu yang dibutuhkan input sebelum ada clock. Input harus sudah ada selama waktu yang tercantum pada data sheet sebelum terjadi clock. Jika input yang diberikan lebih sedikit dari waktu data sheet, maka output akan undefined.

Hold time adalah waktu dibutuhkan input pada suatu keadaan tertentu ( keadaan tetap ) sesudah terjadi clock sesuai dengan waktu yang tercantum pada data sheet agar output dapat terdefinisi jika tidak maka output tidak terdefinisi ( undefined ).

Contoh soal :

Keterangan:

Terdapat output yang XXXX atau don’t care karena :

Bab V

Statik dan Dinamik CMOS

Rangkaian CMOS

Pada dasarnya rangkaian CMOS dibagi menjadi 2 bagian yaitu

· Statik CMOS

· Dinamik CMOS

V.1 Statik CMOS

Untuk rangkaian statik CMOS ini terdiri dari 2 bagian utama yaitu PMOS dan NMOS. Gambaran umum dari statik CMOS ini dapat dilihat dibawah ini :

Pada gambar diatas PUN akan on jika diberi input low, sebaliknya PDN akan on jika diberi input high. Dalam merangkai NMOS dapat diikuti aturan sebagai berikut :

Dari gambar diatas menunjukkan bila rangkaian NMOS disusun secara seri maka sama saja memberi logika AND, bila disusun secara pararel maka akan sama saja dengan memberi logika OR. Begitu juga dengan PMOS mempunyai aturan sebagai berikut :

Dari gambar rangkaian PMOS diatas dapat dilihat arus akan mengalir dari y – x jika complemen dari A di AND dengan complemen dari B. Hal ini sama saja dengan men serikan kedua PMOS. Jika 2 PMOS dipararelkan maka maka arus akan mengalir dari x – y jika complemen dari A OR dengan complemen dari B. PUN ( Pull Up ) ini sering disebut juga sebagai dual dari PDN ( Pull Down ). Hal ini dapat dilihat dari teorema morgan dibawah ini :

Sebagai contoh pada rangkaian NAND Gate kita dapat lihat :

Pada rangkaian diatas dapat dilihat untuk bagian pararel bagian atas merupaka rangkaian PMOS sedangkan pada bagian bawah yang diserikan merupakan bagian NMOS. Untuk lebih jelasnya dapat dilihat pad gambar berikut ini :

Contoh lain adalah rangkaian NOR gate :

Pada rangkaian NOR gate diatas untuk rangkaian PMOS disusun secara seri sedangkan untuk NMOS disusun secara pararel.

CMOS statik ini memiliki beberapa keuntungan yaitu :

· Memiliki noise margin yang tinggi artinya lebih tahan terhadap noise

· Level logicnya tidak bergantung pada ukuran device

· Selalu terhubung dengan Vdd atau GND pada keadaan steady state dan memiliki impedansi yang rendah.

· Tidak power dissipasi

Kekurangan yang dimiliki CMOS statik ini hanya tidak efisien dalam jumlah transistor yang digunakan karena terlalu banyak. Banyaknya transistor yang digunakan sebanyak 2N, dimana N adalah jumlah input.

Cara merangkai CMOS Statik :

Perhatikan contoh dibawah ini :

Pada contoh diatas akan dibuat suatu fungsi seperti diperlihatkan diatas, maka jika kita mengambil yang berlogika satu pada karnaugh map berarti yang akan kita rangkai adalah bagian Pull Up sehingga akan tampak seperti pada gambar yang berwarna hijau begitu juga sebaliknya.

Sebagai contoh akan dibuat rangkaian sebagai

berikut F = ~ (![]() , maka jika kita sederhanakan akan menjadi F =

, maka jika kita sederhanakan akan menjadi F =

![]() . Fungsi ini merupakan fungsi yang digambar dengan PDN ( Pull

Down ), jadi rangkaiannya adalah :

. Fungsi ini merupakan fungsi yang digambar dengan PDN ( Pull

Down ), jadi rangkaiannya adalah :

Setelah didapat rangkaian PUN yaitu pada bagian atas maka untuk PDN tinggal dibalik aja yaitu yang seri jadi pararel dan sebaliknya sehingga terbentuk seperti rangkaian diatas.

Jika kita lihat rangkaian CMOS diatas memiliki jumlah CMOS yang banyak, maka dari ada 3 cara untuk mengurangi jumlah IC CMOS yang digunakan yaitu :

· Resistive Load

Untuk rangkaian dari pengurangan jenis ini adalah sebagai berikut :

Pada rangkaian diatas hanya menggunakan Pull Down saja dimana PDN yang telah kita dapat dari karnaugh map kita serikan dengan resistor.

· Depletion Load NMOS

Pada jenis ini juga tidak jauh berbeda hanya saja diserikan dengan NMOS.

· Pseudo – NMOS

Kalau pada pseudo ini diserikan dengan PMOS.

V.2 Dinamik CMOS

Dynamic CMOS menggunakan NMOS dan dengan penggunaan dynamic maka penggunaan transistor dapat menjadi lebih sedikit karena tidak perlu lagi dibuat pasangannya. Banyaknya transistor yang dibutuhkan adalah N+2.

Selain itu, untuk mengurangi transistor maka ditambahkan clock sehingga untuk fungsi yang sama dapat dihasilkan chip dengan harga yang lebih murah.

Precharge transistor: berfungsi untuk mengisi muatan dan tidak melewati suatu rangkaian.

Evaluation: berfungsi untuk membuang muatan dan melewati suatu rangkaian.

Kekurangan dynamic : pada rangkaian ini diperlukan rangkaian clock sehingga berarti diperlukan transistor lagi.

Ada 2 macam daya :

1. Daya statis : daya yang diperlukan walaupun tidak beroperasi

2. Daya dinamik : daya yang diperlukan jika sedang beroperasi. Dynamic CMOS hanya menggunakan daya dinamik.

CMOS kecepatannya sangat dipengaruhi oleh kapasitor parasit, semakin banyak semakin cepat. Namun bila semakin besar nilai C maka kecepatan makin lambat. Hal ini dikarenakan kapasitansi parasit lebih kecil pada dynamic maka dynamic CMOS lebih cepat. Rangkaian dinamik CMOS ini ada 2 macam yaitu :

· Dengan menggunakan PMOS

· Dengan menggunakan NMOS

Rangkaian dinamik CMOS yang menggunakan PMOS :

Berdasarkan gambaran umum diatas jadi sebagai

contoh jika kita ingin menggambar suatu dinamik CMOS dengan PMOS dengan

persamaan F = ![]() adalah sebagai berikut :

adalah sebagai berikut :

Rangkaian Dinamik CMOS yang menggunakan NMOS :

Gambar diatas adalah gambar dinamik CMOS dengan menggunakan NMOS. Gambar

tersebut merupakan gambaran umumnya. Sebagai contoh jika ingin dibuat suatu

dinamik CMOS dengan F = ![]() maka dapat digambarkan sebagai berikut :

maka dapat digambarkan sebagai berikut :

V.3 Simulasi Cmos static

Nand Gate

F = (A*B)’

Input A = 0, B = 0, F = 1

Input A = 0, B = 1, F = 1

Input A = 1, B = 1, F = 0

Input A = 1, B = 0, F = 1

Pull down

Input A = 0, B = 0, F = 1

Input A = 0, B = 1, F = 1

Input A = 1, B = 1, F = 0

Input A = 1, B = 0, F = 1

Pull Up

Input A = 0, B = 0, F = 1

Input A = 0, B = 1, F = 1

Input A = 1, B = 1, F = 0

Input A = 1, B = 0, F = 1

Pada simulasi ini digunakan frequency 100 Hz dengan duty cycle 25% (Pull Down) dan 80% (Pull Up) karena telah dilakukan uji coba dengan frequency dan duty cycle yang berbeda-beda. Dari percobaan tersebut didapatkan kesimpulan dari program workbench :

1. Semakin kecil duty cycle, semakin semakin kecil Errornya.

2. Semakin besar frequency yang digunakan, tidak ada perubahan yang signifikan pada output.

Uji coba tersebut dapat dilihat pada simulasi berikut ini

frequency = 100 Hz, duty cycle = 25%, Output 2.258 V

frequency = 100 Hz, duty cycle = 20%, Output 1.761 V

frequency = 100 Hz, duty cycle = 50%, Output 3.869 V

Pada simulasi ini terjadi perubahan logika dari 0 ke 1

frequency = 10000 Hz, duty cycle = 20%, Output 0.755 V

Simulasi ini diambil pada saat keadaan telah stabil.

Bab VI

Transmission gate

Circuit special CMOS yang tidak mempunyai bagian counter TTL/ECL adalah transmission gate / bilateral switch, dimana bagiannya disebut single pole, switch single throw dikontrol oleh input dari level logic. Transmisi gate akan melewati signal di kedua arah dan kegunaannya untuk aplikasi digital atau analog.

Figure 8-45(a) adalah penyelesaian dasar untuk bilateral switch. Itu terdiri dari pararel antara P-Mosfet dan N-Mosfet maka kedua polaritas dari input tegangan dapat dialiri listrik. Control input dan sebaliknya digunakan untuk membalikkan saklar maka saklar akan On (closed) dan Off (open). Ketika control tinggi, kedua Mosfet akan mati dan saklar akan tertutup. Ketika control low, kedua Mosfet akan Off dan saklar akan terbuka. Operasi circuit ini seperti “ Electromechanical Relay”. Dalam percobaan, bagaimanapun juga short circuit tidak akan sempurna ketika saklar tertutup. Resistansi saklar ROH = 200 Ω. Di keadaan terbuka, resistansi saklar sangat besar yaitu 1012 Ω. Diamana maksud penting adalah open circuit. Symbol dari figure 8-45(b) digunakan untuk representasi saklar bilateral.

Circuit ini disebut saklar bilateral karena terminal input dan outputnya dapat ditukar. Signal mempergunakan input saklar dapat salah satunya merupakan signal digital atau analog.

Figure 8-46(a) memperlihatkan logic diagram tradisional untuk saklar IC 4016. Dimana juga menggunakan seri 74HC seri 74HC4016. IC berupa 4 saklar bilateral dimana operasinya diuraikan diatas. Masing-masing saklar control bebas dikontrol oleh input sendiri. Sebagai contoh ON/OFF status dari saklar atas di control oleh input CONT. Sejak saklar bidirectional, masing-masing saklar terminal dapat sebagai input/output sebagai label indikasi.

Symbol IC IEEE/ANSI dapat dilihat dari figure 8-46(b). masing-masing segiempat kecil berupa saklar 1 bilateral, tetapi sebagai pemakai hanya segiempat atas berlabel dengan internal notasi IEEE. Melihat segiempat atas control input berlabel X1. Symbol X digunakan untuk menunjuk control input transmisi bidirectional antara nomor terminal input atau output. Angka 1 dari label X1 berindikasi dari transmisi control input antara terminal dengan internal label 1. Diluar segiempat panah double-ended dilihat di terminal saklar untuk menunjuk operasi bidirectional “Horseshoe” digunakan untuk indikasi bahwa terminal ini dapat diatasi oleh signal analog dan tidak membatasi level digital.

Contoh:

Catatan :

Lambang dot ( .) adalah rangkaian seri sedangkan lambang plus ( + ) adalah rangkaian paralel.

VI.1 Rangkaian NAND dengan Transmission Gate ( TGs) and TGlogic

Soal 1 : Dari persamaan berikut ini, gambarkan rangkaiannya!

![]()

Soal : Suatu fungsi ![]() . Buatlah truth Table dan rangkaian nya menggunakan CMOS

Transmission Gate!

. Buatlah truth Table dan rangkaian nya menggunakan CMOS

Transmission Gate!

Jawab :

Truth table

|

A |

B |

F |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

|

1 |

1 |

Soal :

Suatu fungsi ![]() Buatlah truth Table dan rangkaian nya menggunakan CMOS

Transmission Gate!

Buatlah truth Table dan rangkaian nya menggunakan CMOS

Transmission Gate!

Jawab :![]()

![]()

![]()

Truth table

|

A |

B |

C |

F |

|

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

Soal 1 :

Suatu ![]() Buatlah truth Table dan rangkaian nya menggunakan CMOS

Transmission Gate!

Buatlah truth Table dan rangkaian nya menggunakan CMOS

Transmission Gate!

Jawab :![]()

Truth table

|

A |

B |

C |

D |

F |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

Gambar Rangkaian

Dynamic CMOS Design / Domino CMOS Logic

F = AB+C

Model ini jauh lebih hemat dan rumusnya = N + 2

Dynamic CMOS menggunakan NMOS dan dengan penggunaan dynamic maka penggunaan transistor dapat menjadi lebih sedikit karena tidak perlu lagi dibuat pasangannya.

Selain itu, untuk mengurangi transistor maka ditambahkan clock sehingga untuk fungsi yang sama dapat dihasilkan chip dengan harga yang lebih murah.

Precharge transistor : berfungsi untuk mengisi muatan dan tidak melewati suatu rangkaian.

Evaluation : erfungsi untuk membuang muatan dan melewati suatu rangkaian.

Kekurangan dynamic : pada rangkaian ini diperlukan rangkaian clock sehingga berarti diperlukan transistor lagi.

Ada 2 macam daya, yaitu:

CMOS kecepatannya sangat dipengaruhi oleh kapasitor parasit, semakin banyak semakin cepat. Namun bila semakin besar nilai C maka kecepatan makin lambat. Hal ini dikarenakan kapasitansi parasit lebih kecil pada dynamic maka dynamic CMOS lebih cepat.

Dynamic CMOS ada 2 macam :

Rangkaian dynamic CMOS dengan menggunakan PMOS

F = (AB)+(CD)

![]()

4. Dari persamaan berikut ini, gambarkan rangkaiannya!

|

A |

B |

S |

F |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

![]()

VI.2 CMOS Transmission Gates (TGs) and TG Logic.

CMOS transmision gate ini digambarkan seperti pada gambar diatas dimana A sebagai input dan B sebagai output. Jadi output B akan memiliki hasil jika C berlogika 1. Pada saat C = 1 maka B =A. Dengan melihat hal tersebut jadi cara kerja dari CMOS ini adalah mirip dengan switch. Berikut ini adalah contoh – contoh rangkaian CMOS transmission gate :

F = AB + BC

Bab 7

Microelectronics

Rangkaian yang dibuat bukan dalam bentuk PCB melainkan dalam bentuk IC. Hal ini dikarenakan alasan sebagai berikut :

Pembuatan layout didasarkan atas design rule yaitu peraturan design yang dibuat oleh pabrik sehingga keberhasilan pembuatan IC menjadi lebih tinggi. Semakin kecil suatu IC berarti semakin padat chip yang akan dibuat.

Kelebihan dari custom microelectronic

§ Product dibuat rumit agar tidak mudah dicopy.

§ Chip di buat dengan tujuan tertentu ( spesifik ).

§ Tidak menggunakan komponen standart.

§ Hemat daya.

§ Ukuran lebih kecil

§ Lebih mudah di test dan di dokumentasikan.

§ Reabilitas meningkat karena interkoneksi dikurangi.

§ Waktu untuk mendesain dan mendevelop dengan komputer ( CAD ) lebih cepat, tidak harus ke PCB.

§ Harga ( cost ) jauh lebih murah.

Semakin kecil suatu IC berarti semakin padat chip yang akan dibuat.

Jenis – jenisnya adalah sebagai berikut :

· Semua tahapan pabrikasi harus diikuti.

· Paling rumit.

· Paling ekonomis.

· Performance paling tinggi.

· Lebih murah karena dapat dibuat sesuai kebutuhan.

· Proses design-nya paling lama dan disebut hand crafted.

· paling ekonomis

2. Semi custom :

· Tidak semua tahapan pabrikasi harus diikuti

· Harus dilakukan oleh pihak pabrik

Terbagi menjadi dua yaitu :

§ Standard – Cell Techniques

Masih menbuat PMOS dan NMOS tetapi sudah ada pilihan ukuran yang standart

§ Gate – Array Techniques

PMOS dan NMOS sudah jadi, tinggal dirangcang.

3. PLDs (Programmable Device )

Dengan menggunakan program / programmable dan merupakan yang paling mahal.

Terbagi menjadi dua, yaitu :

§ User – Programable

User langsung program dan langsung terhubung.

§ Mask Programmable

User yang program dan untuk menghubungkannya di kirim ke pabrik.

Perbedaan antara standar sel dengan gate array adalah :

Standar sel : berfungsi untuk mengatur semua tahapan.

Gate Array : berfungsi hanya untuk mengatur metal-nya.

Custom Microelectronics :

| Produk dibuat unik agar tidak mudah dikopi. | |

| Chip dibuat dengan tujua khusus. | |

| Tidak menggunakan komponen standar. | |

| Hemat daya. | |

| Ukuran lebih kecil. | |

| Kebebasan untuk berinovasi. | |

| Laebih mudah dites dan didokumantasi. | |

| Reliabilitas meningkat karena interkoneksi dikurangi. | |

| Waktu untuk men-desain dan mengembangkan dengan komputer menjadi lebih cepat. | |

| Cost jauh lebih murah |

Latihan Soal UTS:

1. Analisis rangkaian dibawah dan tentukan gerbang logika yang ekuivalen!

Jawab:

Jika input low, maka ada beda tegangan antara sumber tegangan dan input, sehingga ada arus listrik yang mengalir. Arus ini, sebagai arus base IB, men-trigger transistor sehingga transistor melewatkan arus dari collector ke emitter (short-circuited).

Sebaliknya, jika input high, tidak ada beda tegangan, sehingga arus base IB = 0. Hal ini membuat transistor dalam keadaan tidak bekerja (open-circuited). Pada rangkaian ini, transistor Q7 dan Q9 yang memegang kunci apakah Y bernilai ‘HIGH’ atau ‘LOW’.

Keterangan gambar analisis:

Lingkaran Merah : Transistor dalam keadaan off

LingkaranHijau : Transistor dalam keadaan on

Garis merah putus-putus : Arus IB

Garis merah : Arus IC≈IE atau arus sumber

Kondisi input A=LOW, B=LOW

|

Low |

|

Low |

Perhatikan transistor Q9. Q9 dalam keadaan active, sehingga antara output Y dengan ground terhubung singkat. Sedangkan Q7 dalam keadaan inactive, sehingga antara Vcc dengan Y tidak terhubung (open-circuited). Pada keadaan ini, maka besar tegangan titik Y adalah sama dengan nol (tegangan ground) dan dapat dianggap sebagai kondisi logika ‘LOW’.

Kondisi input A=HIGH, B=LOW

|

High |

|

Low |

Pada keadaan ini, transistor Q7 active, sedangkan Q9 inactive. Oleh karena itu, output Y terhubung singkat langsung dengan Vcc. Jadi, pada kondisi ini, Y mempunyai kondisi logika ‘HIGH’.

Kondisi input A=LOW, B=HIGH

|

Low |

|

High |

Pada keadaan ini, hampir sama dengan kondisi sebelumnya, transistor Q7 active, sedangkan Q9 inactive. Oleh karena itu, output Y terhubung singkat langsung dengan Vcc. Jadi, pada kondisi ini, Y mempunyai kondisi logika ‘HIGH’.

Kondisi input A=HIGH, B=HIGH

|

High |

|

High |

Untuk kondisi kedua input high, transistor Q5 tetap dalam keadaan inactive, sehingga menyebabkan Q6 dan Q7 active. Dalam hal ini, Y terhubung singkat dengan Vcc, sehingga Y mempunyai kondisi logika ‘HIGH’.

Analisis secara keseluruhan dapat disimpulkan dengan truth table dibawah ini:

Truth table untuk analisis no.1

|

Input A |

Input B |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Q7 |

Q8 |

Q9 |

Output Y |

|

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

* High = 1, Low = 0 untuk terminal; active = 1, inactive = 0 untuk Q

Dari table diatas, dapat disimpulkan bahwa rangkaian tersebut ekuivalen dengan gerbang logika OR.

2. Analisis rangkaian dibawah dan tentukan gerbang logika yang ekuivalen!

Jawab:

Jika input low, maka ada beda tegangan antara sumber tegangan dan node input, sehingga ada arus listrik yang mengalir. Arus ini, sebagai arus base IB, men-trigger transistor sehingga transistor melewatkan arus dari collector ke emitter (short-circuited).

Sebaliknya, jika input high, tidak ada beda tegangan, sehingga arus base IB = 0. Hal ini membuat transistor dalam keadaan tidak bekerja (open-circuited). Pada rangkaian ini, transistor Q7 dan Q8 yang memegang kunci apakah Y bernilai ‘HIGH’ atau ‘LOW’.

Keterangan gambar analisis:

Lingkaran Merah : Transistor dalam keadaan off

LingkaranHijau : Transistor dalam keadaan on

Garis merah putus-putus : Arus IB

Garis merah : Arus IC≈IE atau arus sumber

Kondisi input A=LOW, B=LOW, C=LOW

|

Low |

|

Low |

|

Low |

Oleh karena Q7 mendapatkan arus base IB, maka transistor Q7 active. Sedangkan Q8 inactive, disebabkan karena Q4, Q5, atau Q6, yang mensupply arus base Q8, dalam keadaan inactive. Jadi, antara Vcc dengan output Y terjadi short-circuit yang menyebabkan tegangan di Y = Vcc. Dengan kata lain, kondisi logika Y adalah ‘HIGH’.

Kondisi input A=HIGH, B=LOW, C=LOW

|

High |

|

Low |

|

Low |

Pada kondisi ini, Q8 mendapat arus base IB dari sebagian arus emitter Q4 yang active, sehingga Q8 active. Sebaliknya, Q7 menjadi inactive dikarenakan tidak ada arus base Q7 sebab Q4 menarik sebagian besar arus dari Vcc. Dengan aktifnya Q8, maka output Y dengan ground terhubung singkat sehingga Y menjadi ‘LOW’.

Kondisi input A=LOW, B=HIGH, C=LOW

|

Low |

|

High |

|

Low |

Pada kondisi ini, Q8 mendapat arus base IB dari sebagian arus emitter Q5 yang active, sehingga Q8 active. Sebaliknya, Q7 menjadi inactive dikarenakan tidak ada arus base Q7 sebab Q5 menarik sebagian besar arus dari Vcc. Dengan aktifnya Q8, maka output Y dengan ground terhubung singkat sehingga Y menjadi ‘LOW’.

Kondisi input A=LOW, B=LOW, C=HIGH

|

Low |

|

Low |

|

High |

Pada kondisi ini, Q8 mendapat arus base IB dari sebagian arus emitter Q6 yang active, sehingga Q8 active. Sebaliknya, Q7 menjadi inactive dikarenakan tidak ada arus base Q7 sebab Q6 menarik sebagian besar arus dari Vcc. Dengan aktifnya Q8, maka output Y dengan ground terhubung singkat sehingga Y menjadi ‘LOW’.

Kondisi input A=LOW, B=HIGH, C=HIGH,

Kondisi input A=HIGH, B=LOW, C=HIGH,

Kondisi input A=HIGH, B=HIGH, C=LOW, dan

Kondisi input A=HIGH, B=HIGH, C=HIGH

Mempunyai output Y ‘LOW’ karena :

- Q1 selalu berlawanan keadaan dengan Q4

- Q2 selalu berlawanan keadaan dengan Q5

- Q3 selalu berlawanan keadaan dengan Q6

- Jika salah satu atau lebih dari transistor Q4, Q5, atau Q6 active, maka arus sumber akan ditarik oleh transistor tersebut, sehingga arus base Q7 tidak kuat untuk men-drive Q7 untuk active. Jadi, dalam keadaan ini, Q7 selalu inactive.

- Jika dilihat dari koneksi, kaki base Q8 terhubung pada semua kaki emitter dari Q4,5,6, Sehingga jika salah satu Q4, Q5, atau Q6 active, maka otomatis IB dari Q8 dapat dibangkitkan dan Q8 menjadi active.

Analisis secara keseluruhan dapat disimpulkan dengan truth table dibawah ini:

Truth table untuk analisis no.2

|

Input A |

Input B |

Input C |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Q7 |

Q8 |

Output Y |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

* High = 1, Low = 0 untuk terminal; active = 1, inactive = 0 untuk Q

Dari table diatas, dapat disimpulkan bahwa rangkaian tersebut ekuivalen dengan gerbang logika NOR.

3. Analisis rangkaian dibawah dan tentukan gerbang logika yang ekuivalen!

Jawab:

Pada kasus ini, terdapat 3 input yang terhubung langsung dengan satu kaki emitter Q1. Jika salah satu input ini high, maka akan dianggap bahwa kaki emitter mempunyai nilai logika ‘1’. Pada rangkaian ini, transistor Q4 dan Q6 yang memegang kunci apakah Y bernilai ‘HIGH’ atau ‘LOW’.

Keterangan gambar analisis:

Lingkaran Merah : Transistor dalam keadaan off

LingkaranHijau : Transistor dalam keadaan on

Garis merah putus-putus : Arus IB

Garis merah : Arus IC≈IE atau arus sumber

Kondisi input A=LOW, B=LOW, C=LOW

|

Low |

|

Low |

|

Low |

Pada keadaan ini, Q1 active, menyebabkan Q2 inactive, sehingga arus ditarik oleh base Q3 untuk men-drive Q3. Adanya arus yang melewati emitter Q3 akan menghasilkan arus base Q4 sehingga Q4 active. Oleh karena Q2 inactive, maka Q5 dan Q6 tidak mendapat supply arus base dari Q2, sehingga Q5 dan Q6 inactive. Dengan aktifnya Q4, maka antara output Y dengan Vcc terhubung singkat. Hal ini dapat dikatakan Y mempunyai kondisi logika ‘HIGH’.

Kondisi input A=HIGH, B=LOW, C=LOW

|

High |

|

Low |

|

Low |

Pada keadaan ini, Q1 tetap dalam keadaan active. Sesuai penjelasan sebelumnya, maka Q4 active. Dengan aktifnya Q4, maka antara output Y dengan Vcc terhubung singkat. Hal ini dapat dikatakan Y mempunyai kondisi logika ‘HIGH’.

Kondisi input A=LOW, B=HIGH, C=LOW

|

Low |

|

High |

|

Low |

Pada keadaan ini, Q1 tetap dalam keadaan active. Sesuai penjelasan sebelumnya, maka Q4 active. Dengan aktifnya Q4, maka antara output Y dengan Vcc terhubung singkat. Hal ini dapat dikatakan Y mempunyai kondisi logika ‘HIGH’.

Kondisi input A=LOW, B=LOW, C=HIGH

|

Low |

|

Low |

|

High |

Pada keadaan ini, Q1 tetap dalam keadaan active. Sesuai penjelasan sebelumnya, maka Q4 active. Dengan aktifnya Q4, maka antara output Y dengan Vcc terhubung singkat. Hal ini dapat dikatakan Y mempunyai kondisi logika ‘HIGH’.

Kondisi input A=LOW, B=HIGH, C=HIGH,

Kondisi input A=HIGH, B=LOW, C=HIGH, dan

Kondisi input A=HIGH, B=HIGH, C=LOW

Mempunyai output Y ‘HIGH’ karena jika satu atau lebih dari input A, B, atau C memiliki kondisi logika ‘LOW’, maka secara elektris akan mengaktifkan Q1, dan seperti telah dijelaskan sebelumnya, hal ini akan membuat hasil Y menjadi ‘HIGH’.

Kondisi input A=HIGH, B=HIGH, C=HIGH

|

High |

|

High |

|

High |

Pada keadaan ini, Q1 inactive, menyebabkan Q2 active, sehingga tidak ada arus ke base Q3 untuk men-drive Q3 sehingga Q3 inactive. Tidak adanya arus yang melewati emitter Q3 akan menyebabkan Q4 inactive. Oleh karena Q2 active, maka Q5 dan Q6 mendapat supply arus base dari Q2, sehingga Q5 dan Q6 active. Dengan aktifnya Q6, maka antara output Y dengan ground terhubung singkat. Hal ini dapat dikatakan Y mempunyai kondisi logika ‘LOW’.

Analisis secara keseluruhan dapat disimpulkan dengan truth table dibawah ini:

Truth table untuk analisis no.3

|

Input A |

Input B |

Input C |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Output Y |

|

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

* High = 1, Low = 0 untuk terminal; active = 1, inactive = 0 untuk Q

Dari table diatas, dapat disimpulkan bahwa rangkaian tersebut ekuivalen dengan gerbang logika NAND.

4. Analisis rangkaian dibawah dan tentukan gerbang logika yang ekuivalen!

Jawab:

N-Channel MOSFET : active high, yaitu Q2, Q4, Q5, Q9, dan Q11.

P-Channel MOSFET : active low , yaitu Q1, Q3, Q6, Q7, Q8, dan Q10.

Mosfet yang saling berkebalikan keadaan:

Q1-Q2, Q3-Q4, Q8-Q9, Q10-Q11, Q5-Q7

Mosfet yang saling berkebalikan keadaaan dengan input:

A- Q1 dan B-Q3

B-

Mosfet yang sama keadaannya:

Q3 dan Q5

Keterangan gambar analisis:

Lingkaran Merah : MOSFET dalam keadaan off

Lingkaran Hijau : MOSFET dalam keadaan on

Garis merah : Aliran arus ( jalur kondisi ‘High’)

Kondisi input A=LOW, B=LOW

|

Low |

|

Low |

Kedua kondisi input ‘LOW’ mengaktifkan Q1, Q3, dan Q6. Q5 menarik arus dari Q3 sehingga Q5 active yang menyebabkan arus dari Q1 tidak mengalir ke Q8 dan Q9 dan tidak mengalir ke Q7. Tidak adanya arus pada Q8 dan Q9 mengaktifkan Q8 dan menon-aktifkan Q9. Sedangkan Q7 active karena tidak adanya arus yang mengalir ke Gate Q7. Arus mengalir dari VDD melalui Q1-Q5,6, menyebabkan Q10 inactive dan Q11 active. Dalam keadaan ini, output Y terhubung singkat dengan ground dan open-circuited dengan VDD. Hal ini berarti Y mempunyai kondisi logika ‘LOW’.

Kondisi input A=LOW, B=HIGH

|

Low |

|

High |

Pada kondisi ini, Q5 tidak mendapat supply arus dari Q3 (tegangan gate Q5=Gnd karena Q4 active). Demikian juga dengan Q6. Sehingga arus yang berasal dari VDD melalui Q1 yang active, tidak melewati Q5, Q6 melainkan menjadi supply bagi Q8 dan Q9 (menyebabkan Q8 inactive, Q9 active). Walaupun ada kemungkinan arus mengalir dari Q7 yang active, tetapi karena Q8 inactive, arus tidak ada karena open-circuited. Jadi, input bagi Q10 dan Q11 adalah ‘0’, yang membuat Q10 active dan Q11 sebaliknya. Arus dari VDD dapat melalui Q10 dan keluar pada output Y. Dengan demikian, Y ‘HIGH’.

Kondisi input A=HIGH, B=LOW

|

High |

|

Low |