03-06-2006 07:09:28 AM

Catatan Kuliah Elektronika Digital

Bpk. Thomas, S.T., M.T.

Kuliah 1

Dalam perkembangan dunia elektronika, pembuatan chip yang selalu mengalami kemajuan tiap tahunnya seakan sudah menjadi seni. Seni untuk merancang suatu chip yang dari segi biaya, arsitektur, maupun bentuknya merupakan yang terbaik dari waktu ke waktu. Berikut akan dijelaskan cara-cara pembuatan chip :

1.1 Full Custom

Dikatakan full custom karena cara perancangan yang satu ini benar-benar dirancang dari awal . Cara yang satu ini dilakukan melalui pembentukan transistor-transistor untuk membentuk gate-gate yang ingin dibuat dan gate-gate ini dihubungkan sehingga dapat menghasilkan rangkaian yang diinginkan. Proses pembentukan transistor-transistor hingga menjadi gate-gate yang diinginkan dibuat dalam suatu program komputer.

1.2 Semi Custom

Pembuatan chip yang satu ini dibagi menjadi dua cara lagi :

· Standard-cell

Pada perancangan dengan Standard-cell, sel-sel gerbang-gerbang logika ditempatkan dalam bentuk barisan dengan tinggi yang sama dan kemudian dilakukan interkoneksi menggunakan kanal routing untuk membentuk rangkaian yang diinginkan.

· Gate Array

Perancangan dilakukan dengan menghubungkan sel-sel tujuan umum tersebut untuk membentuk rancangan yang diinginkan. Pada perancangan dengan Gate-array, hanya masker metalisasi yang diperlukan dalam memproduksi rancangan, sehingga waktu produksi menjadi singkat dan biaya produksi menjadi lebih murah dibanding dengan perancangan dengan Standard-cell.

1.3 PLD ( Programmable Logical Device )

Jenis pembuatan chip dengan PLD sendiri terbagi 2 yaitu User Programmable dan Mask Programmable Logical Device. Perbedaan utama kedua jenis ini adalah MPLD diprogram menggunakan proses pabrikasi untuk membentuk interkoneksi metal, sedangkan pada PLD yang user-programmable dilakukan dengan memprogram secara elektrik menggunakan saklar terprogram (programmable switch).

Kuliah 2

Lebih lanjut dalam bahasan ini penulis akan menjabarkan tentang FPLD dan MPLD. FPLD merupakan sebuah divais standar yang dapat diprogram oleh pengguna untuk mendapatkan fungsi yang diinginkan.

Dari sisi kecepatan, MPLD lebih cepat dibandingkan dengan FPLD, mengingat pada FPLD memakai saklar terprogram yang dapat menambah resistansi dan kapasitansi pada path internal. Dari sisi kecepatan, FPLD masih dapat menangani hampir semua aplikasi yang ada.

Dengan FPLD, untuk mendapatkan rancangan dengan kecepatan yang lebih tinggi dapat dilakukan hanya dengan mengganti divais target yang lebih cepat, dan tidak perlu modifikasi rancangan. Sedangkan pada MPLD diperlukan masker baru yang mengikuti teknologi proses yang dipakai.

FPLD mempunyai kelebihan pada biaya prototyping yang murah, sedangkan pada MPLD mempunyai kelebihan pada biaya produksi per unit murah. Untuk mendapatkan kedua kelebihan ini sekaligus dapat dilakukan prototyping dengan FPLD, kemudian produksinya dilakukan dengan MPLD. Hal ini dapat dilakukan mengingat beberapa FPLD vendor memberikan fasilitas mask-programmed versions untuk FPLD-nya.

Langkah pertama dalam perancangan dengan FPLD adalah capture rancangan (Design Entry) yang dapat dilakukan secara skematik, persamaan Boolean, state machine, dan bahasa perancangan perangkat keras HDL (Hardware Description Language ) seperti AHDL(Altera Hardware Description Language) , VHDL (Very High Speed Integrated Circuit Hardware Description Languange) dan Verilog. Setiap bagian rancangan dapat dibuat dengan cara yang berbeda dan bagian-bagian rancangan tersebut dapat digabungkan dengan berbagai cara juga, yaitu dengan skematik dan bahasa perancangan perangkat keras HDL.

Kuliah 3

KARAKTERISTIK IC DIGITAL CMOS

Ø Tegangan input dimana logika high / 1 ( Vih ).

Tegangan input minimum yang dikenal sebagai logika 1 = 3,5 V; Vss = 5 V.

Ø Tegangan input dimana logika low / 0 ( Vil ).

Tegangan input maksimum yang dikenal sebagai logika 0 = 1,5 V; Vss = 5 V.

Ø Tegangan output dimana logika high / 1 ( Voh ).

Tegangan output minimum yang bisa dikirim sebagai logika 1 = 4,99 V; Vss = 5 V.

Ø Tegangan output dimana logika low / 0 ( Vol ).

Tegangan output maksimum yang bisa dikirim sebagai logika 0 = 0,01 V; Vss = 5 V.

Ø Arus input dimana logika high / 1 ( Iih ).

Arus input minimum yang dibutuhkan agar logika tetap 1 = + 10 pA; Vss = 5 V; Vin = 3,5 V.

Ø Arus input dimana logika low / 0 ( Iil ).

Arus input maksimum agar logika tetap 0 = - 10 pA maksimum; Vss = 5 V; Vin = 1,5 V.

Ø Arus output dimana logika high / 1 ( Ioh ).

Arus output maksimum yang bisa dihasilkan untuk logika 1 = - 0,5 mA maksimum; Vss = 5 V; Vin = 3,5 V.

Ø Arus output dimana logika low / 0 ( Iol ).

Arus output maksimum yang bisa dimasukkan untuk logika 0 = + 0,4 mA maksimum; Vss = 5 V; Vin = 1,5 V.

Kuliah 4

Parameter Tes Umum untuk TTL Devices

Logika High Tegangan Input, Vih (Logika “1”)

· Ini adalah tegangan minimum untuk sebuah IC Digital TTL agar dikenali sebagai logika bernilai “1”.

· Spesifikasi standar : minimum 2.0 V

Logika Low Tegangan Input, Vil (Logika “0”)

· Ini adalah tegangan maksimum untuk sebuah IC Digital TTL agar dikenali sebagai logika bernilai “0”.

· Spesifikasi standar : maksimal 0.8 Volt

Logika High Tegangan Output,Voh (Logika “1”)

· Ini adalah tegangan minimum untuk sebuah IC Digital TTL untuk menghasilkan logika bernilai “1”.

· Spesifikasi standar : minimal 2.4 Volt

Logika Low Tegangan Output, Vol (Logika “0”)

· Ini adalah tegangan maksimum untuk sebuah IC Digital TTL untuk menghasilkan logika bernilai “0”.

· Spesifikasi standar : maksimal 0.4 Volt

Logika High Arus Input, Iih

· Ini adalah jumlah arus minimum yang dibutuhkan oleh input sebuah IC Digital TTL untuk tetap berada pada logika bernilai “1”..

· Contoh dari spesifikasi nyata : minimum +10 μA ketika Vcc=Max dan Vin=2.7 V.

Logika Low Arus Input, Iil

· Ini adalah jumlah arus maksimum yang dibutuhkan oleh input sebuah IC Digital TTL untuk tetap berada pada logika bernilai “0”..

· Contoh dari spesifikasi nyata : minimum -1.6 mA ketika Vcc=max dan Vin=0.5 V.

Arus Output Short Circuit, Ios

· Ini adalah jumlah arus dapat digunakan oleh output sebuah IC Digital TTL yang di-short-kan.

· Contoh dari spesifikasi nyata : minimum -40 mA, standar -65 mA, maksimum -100 mA ketika Vcc=max dan Vout=0 V.

Arus Supply, Icc

· Ini adalah suplai arus yang dibutuhkan oleh sebuah IC TTL.

· Contoh dari spesifikasi nyata : minimum 30 mA, maksimum 50 mA ketika Vcc=max.

Kuliah 5

Tegangan dan Arus pada TTL

Ø Arus input level low = Iil = 1,6 mA ( -1600 µA ).

Ø Arus input level high = Iih = 40 µA.

Ø Iol-Arus output level low = 16 mA ( 16000 µA ).

Ø Ioh-Arus output level high = -400 A ( -800 µA ).

DC Noise Margin

( untuk TTL tipe 74xx )

Ø Vdd = 5 V.

Ø Voh min = 2,4 V.

Ø Vih min = 2,0 V.

Ø Vol max = 0,4 V.

Ø Vil max = 0,8 V.

Ø High state DC noise margin = Voh min - Vih min = 2,4 –2,0 = 0,4 V.

Ø Low state DC noise margin = Vil max - Vol max = 0,8 –0,4 = 0,4 V.

Kuliah 6

Logic Circuit

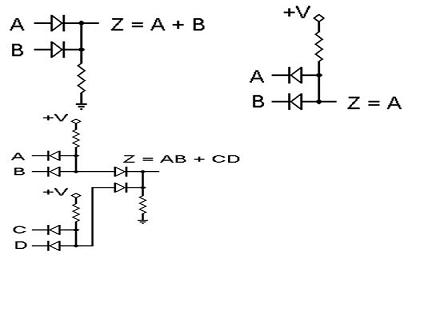

Diode Logic

RANGKAIAN RTL DAN DTL

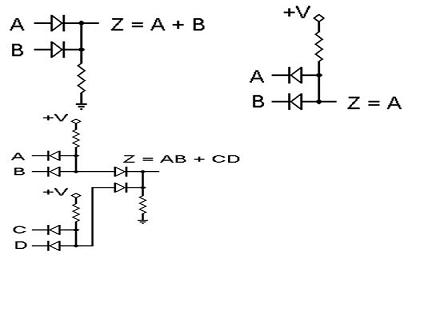

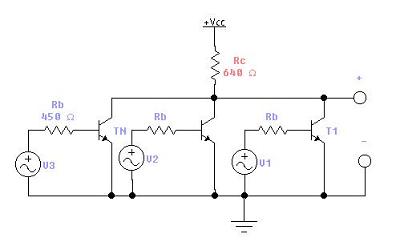

Gerbang Dasar Resistor Transistor Logic ( RTL )

Gambar 1.1 Suatu masukan gerbang RTL

Suatu gerbang RTL terdiri dari N transistor yang emitternya dihubungkan ke ground dan collectornya terhubung melelui tahanan collector yang sama kecatu daya. Tegangan input Vi ( i =1,2,N) menggambarkan level logika yang diberikan pada bese melalui tahanan Rb. Bila kita mangambil logika positif, gerbang memperlihatkan logika NOR.

|

V1 |

V2 |

V0 |

|

V1 |

V2 |

V0 |

|

L L H H |

L H L H |

H L L L |

0 0 1 1 |

0 1 0 1 |

1 0 0 0 |

Tabel 1.1 Logika NOR

Pada logika positif, “false” = 0 pada masukkan agar membuat transistor cut-off. VH adalah tegangan yang diberikan pada masukkan untuk membuat transistor saturasi. VL disini harus kurang dari tegangan tertentu dan VH harus lebih besar dari tegangan tertentu. Dalam hal ini VL < VH, tegangan cut-in dan VH > tegangan yang diberikan pada Rb yang membawa transistor pada keadaan saturasi.

Setiap input diimplementasikan dengan satu resistor dan satu transistor. Kolektor-kolektor dari masing-masing transistor dihubungkan menjadi satu pada output. Besar tegangan untuk rangkaian adalah 0,2 V untuk level low dan mulai 1 sampai 3,6 V untuk level high.

Analisis dari gerbang RTL sangat sederhana. Jika ada satu input gerbang RTL yang high, maka transistor yang bersangkutan akan menuju ke keadaan saturasi. Hal ini menyebabkan output akan low, tanpa perlu melihat keadaan transistor lain. Jika semua input low yaitu sekitar 0,2 V, maka semua transistor akan dalam keadaan cut off karena VBE < 0,6 V. Hal ini akan menyebabkan output dari rangkaian akan high, dengan besar tegangan mengacu pada tegangan VCC.

Gerbang Dasar Dioda Transistor Logic ( DTL )

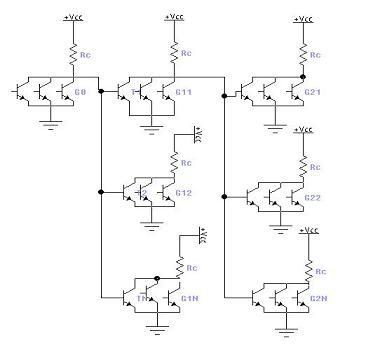

Dengan menghilangkan Rb pada rangkaian RTL maka terjadi Direct Coupled Transistor Logic (DCTL). Disebut DCTL karena masukkan dibuat langsung pada base. Seperti pada RTL diatas, DCTL ini merupakan logika NOR DTCL yang tidak banyak dipergunakan. Logika NOR mempunyai fungsi yang lengkap sehingga bermacam-macam logika dapat dibuat dengan memakai gerbang logika NOR. Di dalam system switching maka suatu input dari gerbang NOR dapat digerakan oleh keluaran dari gerbang NOR yang sama. Sebaliknya suatu gerbang NOR dapat dipakai untuk menggerakan masukkan gerbang Nor lainnya. Dalam hal ini contohnya adalah G11 pada gambar 1.2.

G11 menerima masukkan dari G0yang juga memberi sinyal pada salah satu masukkan dari gerbang (N-1) lainnya, yakni gerbang G12 sampai G IN. G11 ini juga memberikan sinyal pada salah satu dari gerbang N lainya, yakni G 21 sampai G 2N. gerbang-gerbang lainnya mendapat masukkan dari sumber lain yang tidak digambarkan pada gambar. Bila gerbang ini mempunyai kelebihan masukkan yang tidak dipergunakan, maka masukkan yang tidak dipergunakan harus digroundkan sehingga transistor yang bersangkutan akan berada pada cut-off dan tidak mempunyai pengaruh pada operasi gerbang.

Gambar 1.2 Gerbang DCTL NOR dengan N Fan-Out

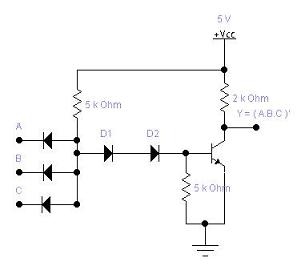

Rangkaian dasar dalam keluarga logika digital DTL adalah gerbang NAND. Tiap input diasosiasikan dengan sebuah dioda. Dioda dan resistor 5 kΩ membentuk sebuah gerbang AND. Transistor berperan sebagai penguat arus sambil meng-invert sinyal digital. Untuk logika low adalah sekitar 0,2 V dan untuk logika high adalah sekitar 4 sampai 5 V.

Jika salah satu input berlogika low atau sekitar 0,2 V, maka dioda input yang bersangkutan akan mengalirkan arus dari VCC dan melewati resistor 5 kΩ menuju input. Tegangan pada titik P adalah sama dengan tegangan input 0,2 V ditambah tegangan jatuh dioda 0,7 V, sehingga totalnya adalah 0,9 V. Agar transistor mulai aktif, tegangan pada titik P harus sekitar tegangan VBE ditambah tegangan jatuh dioda D1 dan D2 atau 3 X 0,6 V = 1,8 V. Karena tegangan pada titik P adalah sekitar 0,9 V, maka transistor dalam keadaan cut off dan output berlogika high atau sekitar 5 V.

Jika semua input dari gerbang adalah high, maka transistor akan menuju keadaan saturasi karena tegangan P sekarang sama dengan VBE ditambah tegangan jatuh D1 dan D2 atau 0,7 V X 3 = 2,1 V. Semua input dioda dalam keadaan reverse bias dan mati. Arus basis cukup besar untuk membuat transistor menuju ke keadaan saturasi, meskipun arus basis berkurang karena resistor 5 kΩ. Dengan keadaan transistor saturasi maka tegangan output akan jatuh menjadi sekitar VCE atau 0,2 V yang berarti logika low.

Kuliah 7

CMOS ( Complementary Metal Oxide Semiconductor )

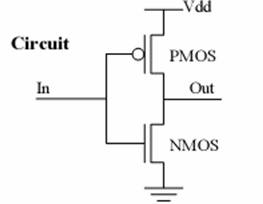

Cara kerja dari inverter transistor MOS :

1. MOS n-chanel adalah saat gerbang nya ke sumber tegangan adalah positif.

2. MOS p-chanel adalah saat gerbang nya ke sumber tegangan adalah negative.

3. Tipe lainnya mati apabila tegangan dari gerbang ke sumber adalah nol.

Cara kerja dari inverter : Saat masuk rendah, kedua gerbang adalah nol. Masukan adalah pada VDD sehubungan dengan sumber dari p-chanel dan saat itu 0 V sehubungan dengan sumber n-chanel alat mati. Berdasar kondisi diatas mengakibatkan impedansi yang rendah alur Dari VDD ke keluaran dan impedansi yang tinggi dari keluaran ke ground. Oleh karena itu keluaran tegangan VDD tingkat tinggi di bawah kondisi-kondisi pemuatan normal. Saat masuk tinggi kedua-duanya gerbang adalah pada Vdd dan situasi dibalikkan, p-chanel mati dan n-chanel nyala. Hasilnya keluaran mendekati tingkatan rendah adalah 0.

Pada dasarnya rangkaian CMOS dibagi menjadi 2 bagian yaitu

· Statik CMOS

· Dinamik CMOS

Statik CMOS

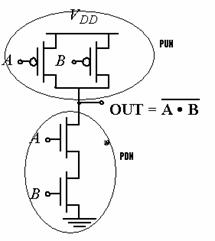

Untuk rangkaian statik CMOS ini terdiri dari 2 bagian utama yaitu PMOS dan NMOS. Gambaran umum dari statik CMOS ini dapat dilihat dibawah ini :

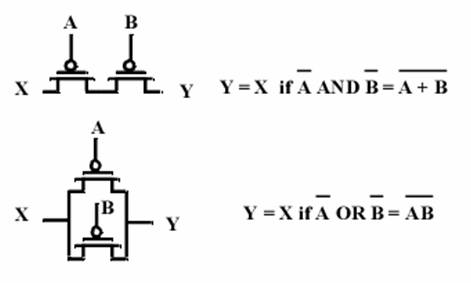

Pada gambar diatas PUN akan on jika diberi input low, sebaliknya PDN akan on jika diberi input high. Dalam merangkai NMOS dapat diikuti aturan sebagai berikut :

Dari gambar diatas menunjukkan bila rangkaian NMOS disusun secara seri maka sama saja memberi logika AND, bila disusun secara pararel maka akan sama saja dengan memberi logika OR. Begitu juga dengan PMOS mempunyai aturan sebagai berikut :

Dari gambar rangkaian PMOS diatas dapat dilihat arus akan mengalir dari y – x jika complemen dari A di AND dengan complemen dari B. Hal ini sama saja dengan men serikan kedua PMOS. Jika 2 PMOS dipararelkan maka maka arus akan mengalir dari x – y jika complemen dari A OR dengan complemen dari B. PUN ( Pull Up ) ini sering disebut juga sebagai dual dari PDN ( Pull Down ). Hal ini dapat dilihat dari teorema morgan dibawah ini :

Sebagai contoh pada rangkaian NAND Gate kita dapat lihat :

Pada rangkaian diatas dapat dilihat untuk bagian pararel bagian atas merupaka rangkaian PMOS sedangkan pada bagian bawah yang diserikan merupakan bagian NMOS. Untuk lebih jelasnya dapat dilihat pad gambar berikut ini :

Contoh lain adalah rangkaian NOR gate :

Pada rangkaian NOR gate diatas untuk rangkaian PMOS disusun secara seri sedangkan untuk NMOS disusun secara pararel.

statik ini memiliki beberapa keuntungan yaitu :

· Memiliki noise margin yang tinggi artinya lebih tahan terhadap noise

· Level logicnya tidak bergantung pada ukuran device

· Selalu terhubung dengan Vdd atau GND pada keadaan steady state dan memiliki impedansi yang rendah.

· Tidak power dissipasi

Kekurangan yang dimiliki CMOS statik ini hanya tidak efisien dalam jumlah transistor yang digunakan karena terlalu banyak. Banyaknya transistor yang digunakan sebanyak 2N, dimana N adalah jumlah input.

Cara merangkai CMOS Statik :

Perhatikan contoh dibawah ini :

Pada contoh diatas akan dibuat suatu fungsi seperti diperlihatkan diatas, maka jika kita mengambil yang berlogika satu pada karnaugh map berarti yang akan kita rangkai adalah bagian Pull Up sehingga akan tampak seperti pada gambar yang berwarna hijau begitu juga sebaliknya.

Sebagai contoh akan dibuat rangkaian

sebagai berikut F = ~ ( ![]() ),

maka jika kita sederhanakan akan menjadi F =

),

maka jika kita sederhanakan akan menjadi F =

![]() .

Fungsi ini merupakan fungsi yang digambar dengan PDN ( Pull Down ), jadi

rangkaiannya adalah :

.

Fungsi ini merupakan fungsi yang digambar dengan PDN ( Pull Down ), jadi

rangkaiannya adalah :

Setelah didapat rangkaian PUN yaitu pada bagian atas maka untuk PDN tinggal dibalik aja yaitu yang seri jadi pararel dan sebaliknya sehingga terbentuk seperti rangkaian diatas.

Kuliah 8

Emitter-Coupled Logic

ECl yang didesain dengan kemampuan bekerjanya sangat cepat tetapi memerlukan daya yang sangat besar juga.

ECL hanya bekerja di cutoff dan aktif sedangkan DTL/TTL hanya bekerja di cutoff sampai saturated.

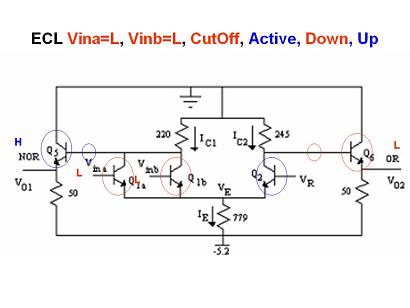

ECL Vina=L, Vinb=L, Cutoff, Active, Down, Up

Vina=L dan vinb=L --> Q1a dan Q1b cutoff --> IbQ5 up --> Q5 active --> V01=H

Q1a dan Q1b cutoff --> Q2 active --> Ib Q6 down --> Q6 cutoff --> V02=L

ECL Vina=H, Vinb=L, CutOff, Active, Down, Up

Vin a=H dan Vin b=L --> Q1a aktif, Q1b cutoff --> IbQ5 down --> Q5 cutoff --> V01=L

Q1a aktif Q1b cutoff --> Q2 cutoff --> IbQ6 up Q6 aktif --> V02=H

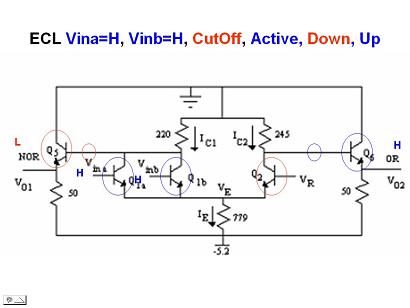

ECL Vina=H, Vinb=H, CutOff, Active, Down, Up

Vina=H dan Vinb=H --> Q1a aktif, Q1b aktif --> IbQ5 down --> Q5 cutoff --> V01=L

Q1a aktif,Q1b aktif --> Q2 cutoff --> IbQ6 up --> Q6 aktif --> V02=H

ECL mempunyai perubahan output sampai 0,85 volt dari yang terendah –1,6 volt dan tertinggi –0,75.

Ada 4 jenis logic dalam keluarga chip diantaranya:

1. Bi-polar

Dalam Bi-Polar dapat diketahui dengan jenis tipe 74xx, 74S, 74LS, 74AS, 74ALS, 74F....

2. CMOS

Dalam Bi-Polar dapat diketahui dengan jenis tipe 74AC, 74ACT ,74LCX ,74LVX ,74LVQ.

3. ECL

Alat ini terdiri dari 10 K, 100 K, atau seri 10 E (EcLinPS).

4. BiCMOS

Alat ini terdiri dari ABT, BCT, dan sebagainya.

Kuliah 9

CMOS STATIS

Simbol

:

Simbol

:

NMOS Circuit PMOS Circuit

Tanda bubble digambat pada gerbang gate PMOS untuk menunjukkan bahwa polaritas PMOS dan NMOS terbalik.

Model Switch Transistor PMOS

Switch Open jika Drain (D) tidak dihubungkan dari Source (S) pada saat VG = VDD

Switch Closed jika Drain (D) dihubungkan pada Source (S) ketika VG = 0

Model Switch Transistor NMOS

Pull-Down NMOS dan PMOS

Pull-Up NMOS dan PMOS

Rangkaian CMOS statis adalah sebagai berikut :

PUN dan PDN adalah Dual Networks

Hubungan Seri/Paralel pada Transistor NMOS

Transistor dapat dianggap sebagai switch yang dikontrol oleh sinyal pada Gate (G). NMOS akan berada pada keadaan closed apabila input high.

Hubungan Seri/Paralel pada Transistor PMOS

PMOS akan berada pada keadaan closed apabila input low.

CMOS

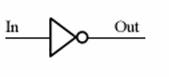

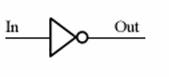

INVERTER

Simbol :

Sirkuit

:

Sirkuit

:

Operasi

Inverter :

Operasi

Inverter :

Input = low (0)

Output = high (1)

Input = high (1)

Output = low (0)